Cirrus Logic CS1810xx User Manual

Page 49

CobraNet Hardware User’s Manual

Mechanical Drawings and Schematics

DS651UM23

©

Copyright 2005 Cirrus Logic, Inc.

49

Version 2.3

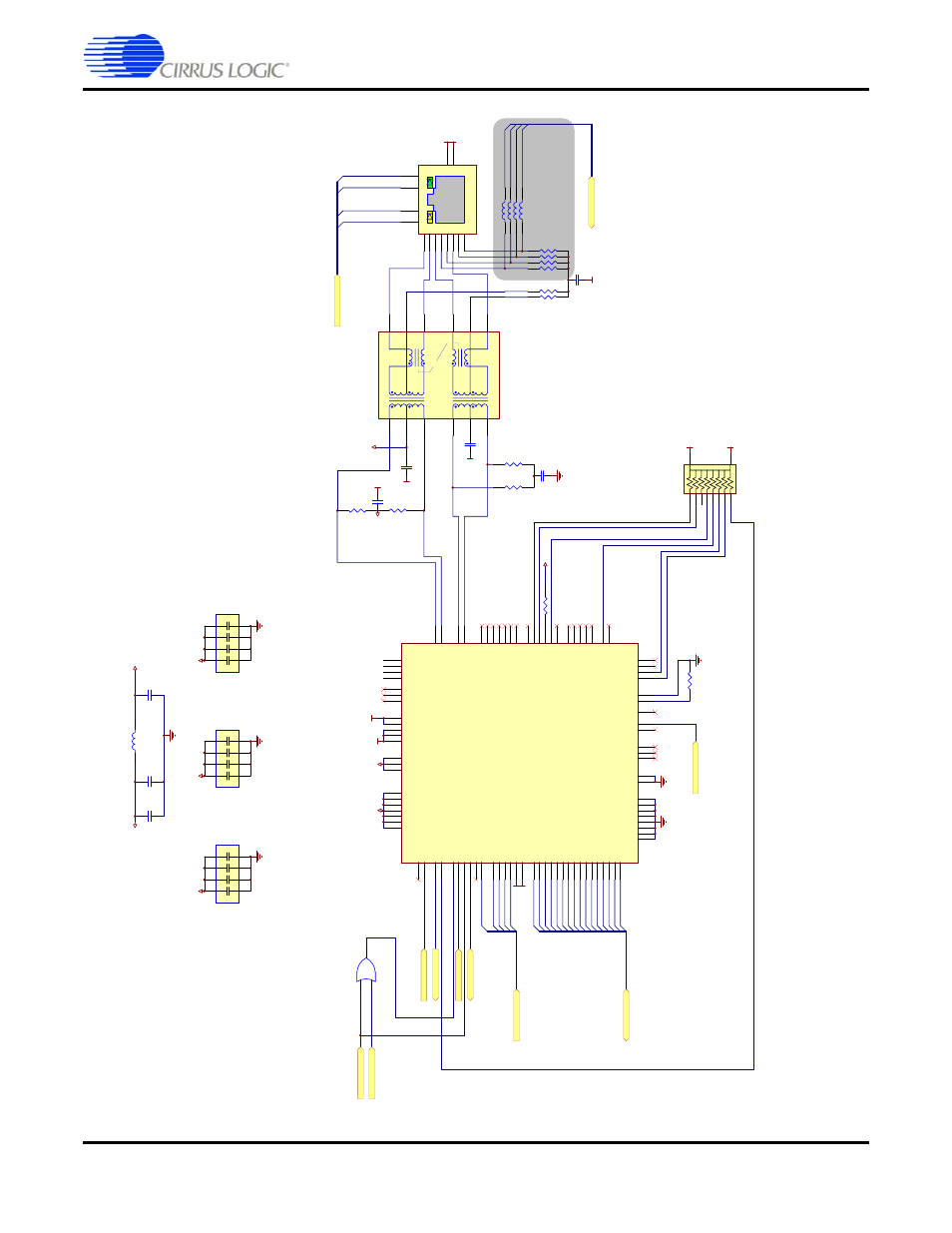

Figure 29. CM-2 RevF Schematic Page 6 of 7

IO

R

#

1

IO

W

#

2

AEN

3

IO

W

A

IT

4

DVDD

5

SD0

6

SD1

7

SD2

8

SD3

9

SD4

10

SD5

11

SD6

12

SD7

13

RST

14

DGND

15

TEST1

16

TEST2

17

TEST3

18

TEST4

19

DVDD

20

X2_25M

21

X1_25M

22

DGND

23

SD

24

BGGND

25

BGRES

26

AVDD

27

AVDD

28

RXI

+

29

RXI

-

30

AGND

31

AGND

32

T

XO+

33

T

XO-

34

AVDD

35

DVDD

36

LIN

K

_

I

37

RXD0

38

RXD1

39

RXD2

40

RXD3

41

DGND

42

CRS

43

COL

44

RX_DV

45

RX_ER

46

RX_CL

K

47

TEST5

48

TX

_

C

LK

49

T

XD0

50

T

XD1

51

T

XD2

52

T

XD3

53

TX

_

E

N

54

DVDD

55

MD

IO

56

MD

C

57

DGND

58

CLK20MO

59

SPEED#

60

DUP#

61

LINKACT#

62

DGND

63

EEDI

64

EEDO

65

EECK

66

EECS

67

GPIO0

68

GPIO1

69

GPIO2

70

GPIO3

71

DVDD

72

DVDD

73

NC

74

NC

75

DGND

76

NC

77

LIN

K

_

O

78

WA

KE

U

P

79

PW

_RST

#

80

DGND

81

SD15

82

SD14

83

SD13

84

SD12

85

SD11

86

SD10

87

SD9

88

SD8

89

DVDD

90

IO

1

6

91

CM

D

92

SA4

93

SA5

94

SA6

95

SA7

96

SA8

97

SA9

98

DGND

99

IN

T

100

U8

DM

9000

R23

49.

9 Ohm

, 1%

R24

49.

9 Ohm

, 1%

R21

R22

49.9 Ohm, 1%

R26

6.

8K

Ohm

, 1%

C30

0.

1 uF

C31

0.

1 uF

C32

0.

1 uF

C29

0.

1 uF

K

eep r

es

clos

e to chip pins

.

GN

D

VCC_PHY2

GN

D

R34

75 Ohm

, 1%

R33

R35

R36

R37

R38

75 Ohm

, 1%

FB

8

FB

9

FB

1

0

FB

1

1

F

B

EAD,

68 Ohm

@

100 M

H

z

C49

0.

01 uF

, 2K

V

Note: See Text W

a

rning

W

arning

: Failure to

properly

ins

tall and

conf

ig

ur

e the aux.

E

ther

n

et s

ig

n

als

can r

es

u

lt in

v

er

y

bad thing

s (

i.

e.

, f

ir

e,

s

m

ok

e,

bad hair

day

s)

.

I

f pow

er

is

s

u

pplied v

ia the R

J-

45 connector

then

only

the f

errite beads

are installed (not the

r

es

is

tor

s)

. I

f pow

er

is

not s

upplied v

ia the R

J-

4

5

then the r

es

is

tor

s ar

e ins

talled and the beads

ar

e

not.

VCC_PHY2

VCC_+

3

.3

VCC_+

3.

3

VCC_+

3.

3

DAT

A0

DAT

A1

DAT

A2

DAT

A3

DAT

A4

DAT

A5

DAT

A6

DAT

A7

DAT

A8

DAT

A9

DAT

A10

DAT

A11

DAT

A12

DAT

A13

DAT

A14

DAT

A15

ADDR[

0.

.19]

DAT

A[

0.

.15]

ADDR[

0.

.19]

DAT

A[

0.

.15]

HRESET

_B

UF

#

VCC_+

3

.3

GN

D

WE

#

M

AC_CS#

IO

W

A

IT

HRESET

_B

UF

#

WE

#

IO

W

A

IT

MA

C

_

IR

Q

1

MA

C

_

IR

Q

1

T

h

e secondary

E

thernet M

A

C

a

nd connector are optional.

If

it is not required then all pa

rts on this pag

e can be depopulated

(or rem

oved entirely

f

rom

a new

desig

n based on this circuit).

ADDR0

ADDR2

ADDR3

ADDR1

ADDR4

VCC_+

3

.3

VCC_PHY2

C47

0.

01 uF

FB

7

F

B

EAD,

68 Ohm

@

100 M

H

z

C8

10 uF

, X5R,

6.

3 Vo

lt

s

C9

10 uF

, X5R,

6.

3 Vo

lt

s

VCC_+

3

.3

VCC_PHY2

1

2

3

4

5

6

7

8

CN11

0.

1 uF

, 4x Array

1

2

3

4

5

6

7

8

CN9

0.

1 uF

, 4x Array

VCC_+

3

.3

1

2

3

4

5

6

7

8

CN10

0.

1 uF

, 4x Array

GN

D

1

2

3

4

5

6

7

8

9

10

RN8

3.

3K

Ohm

, 8x Array

GN

D

CLK_25

CL

K

_25

VCC_PHY2

OE#

M

AC_CS#

OE#

M

AC_CS#

12

13

11

U10D

74L

VC32

R52

3.

3K

Ohm

VCC_+

3

.3

1

2

3

4

5

6

7

8

S1

S2

L1

L2

L3

L4

J6

RJ

45

1

2

3

4

5

6

19

20

21

22

23

24

TX

D

+

TX

D

-

T

XD+

T

XD-

RXD+

RXD+

RXD-

RXD-

T1

A

H2006A

GN

D

SHI

E

L

D

SHI

E

L

D

SHI

E

L

D

L

E

D

_

B

U

F

[0

..7

]

L

E

D

_

B

U

F

[0

..7

]

AUX_POW

ER0

AUX_POW

ER1

AUX_POW

ER2

AUX_POW

ER3

AUX_POW

ER[

0

..

3

]

AUX_POW

ER[

0

..

3

]

LED_BUF4

LED_BUF5

LED_BUF6

LED_BUF7