3 standard mode data timing, Cs18100x/cs49610x, cs18101x/cs49611x, Cs18102x/cs49612x – Cirrus Logic CS1810xx User Manual

Page 22

22

©

Copyright 2005 Cirrus Logic, Inc.

DS651UM23

Version 2.3

CobraNet Hardware User’s Manual

Digital Audio Interface

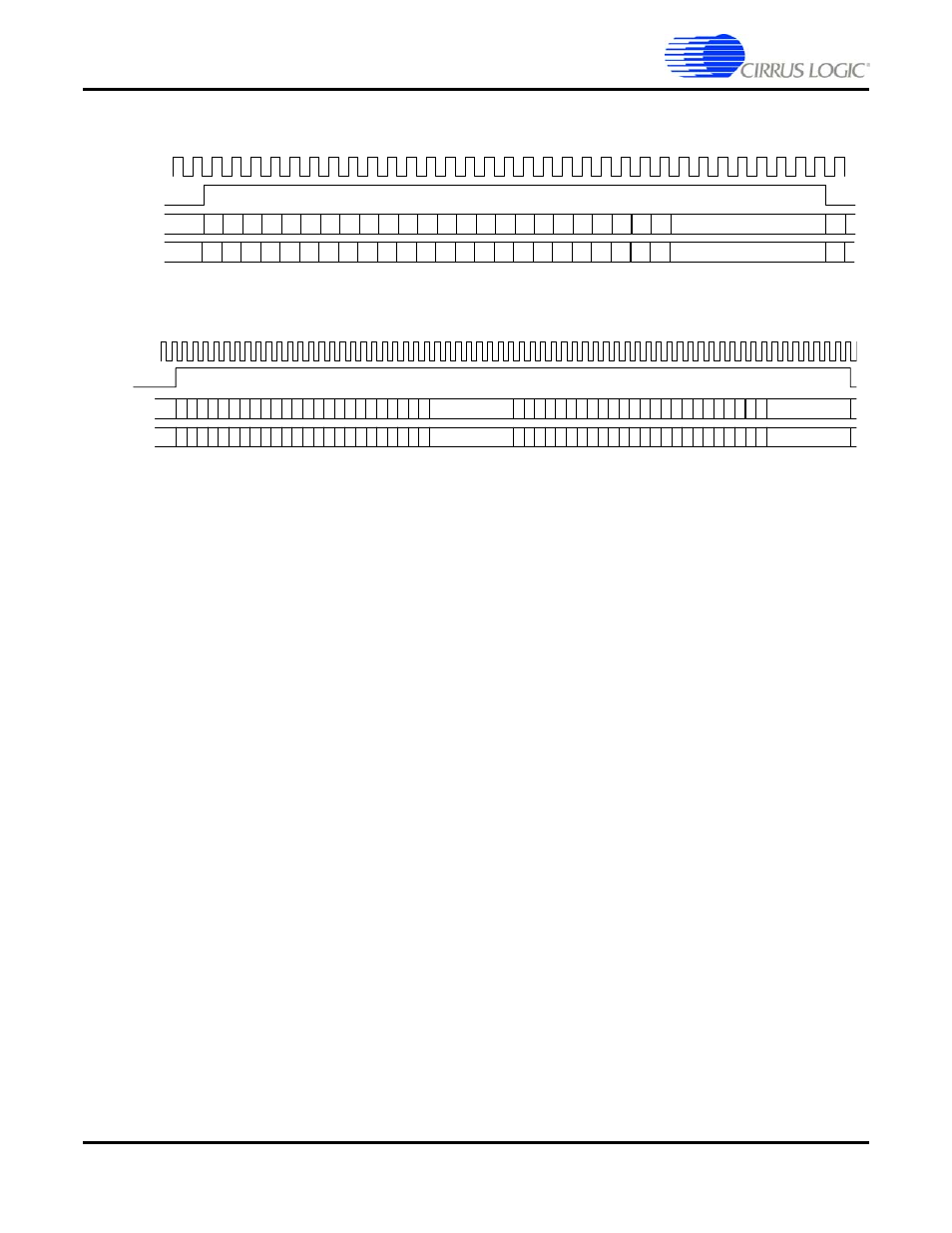

6.1.3 Standard Mode Data Timing

Figure 12. Audio Data Timing Detail - Standard Mode, 64FS - CS18100x/CS49610x, CS18101x/CS49611x

Figure 13. Audio Data Timing Detail - Standard Mode, 128FS - CS18102x/CS49612x

Each audio channel is comprised of 32 bits of data, regardless of audio sample size. The

figure above shows 24-bit audio data.

The MSB is left justified and is aligned with FS1. Data is sampled on the rising edge of

DAI_SCLK and data changes on the falling edge.

FS1

DAI1_DATAx

DAO1_DATAx

DAI1_SCLK

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

23

1

0

Unused

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

23

1

0

Unused

FS1

DAI1_DATAx

DAO1_DATAx

DAI1_SCLK

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2

23

1 0

Unused

22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2

23

1 0

Unused

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2

23

1 0

Unused

22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2

23

1 0

Unused