1 digital audio interface timing – Cirrus Logic CS1810xx User Manual

Page 20

20

©

Copyright 2005 Cirrus Logic, Inc.

DS651UM23

Version 2.3

CobraNet Hardware User’s Manual

Digital Audio Interface

Although data is always transmitted and received with a 32-bit resolution by the

synchronous serial ports, the resolution of the data transferred to/from the Ethernet may

be less. Incoming audio data is truncated to the selected resolution. Unused least

significant bits on outgoing data is zero filled.

6.1

Digital Audio Interface Timing

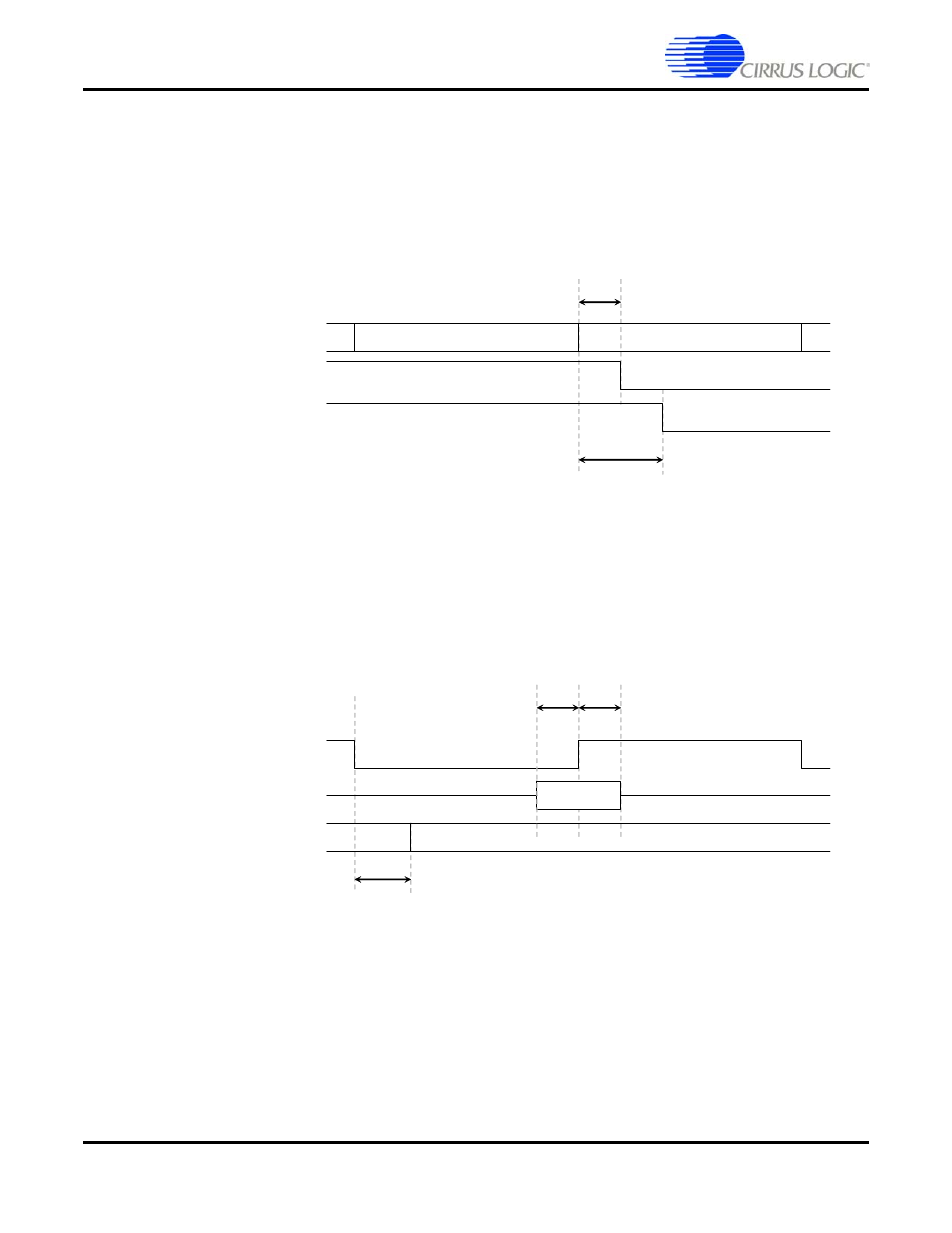

Figure 6. Timing Relationship between FS512_OUT, DAO1_SCLK and FS1

An DAO1_SCLK edge follows an MCLK_OUT edge by 0.0 to 5.0ns. An FS1 edge follows

a MCLK_OUT edge by 0.0 to 10.0ns.

Note: The DAO1_SCLK and FS1 might be synchronized with the either the falling edge or

the rising edge of MCLK_OUT. Which edge is impossible to predict since it depends

on power up timing.

Figure 7. Serial Port Data Timing Overview

Setup times for DAI1_DATAx and FS1 are 5.0 ns with a hold time of 0.0 ns with respect to

the DAI1_SCLK edge. Clock to output times for DAO1_DATAx is 0.0 to 12.0 ns from the

edge of DAO1_SCLK.

MCLK_OUT

DAO1_SCLK

FS1

0 – 5ns

0 – 10ns

DAI1_DATAx

DAO1_SCLK

0 – 12ns

DAO1_DATAx

≥5ns

≥0ns