0 synchronization, 1 synchronization modes, Figure 3. audio clock sub-system – Cirrus Logic CS1810xx User Manual

Page 17: Synchronization" on

CobraNet Hardware User’s Manual

Synchronization

DS651UM23

©

Copyright 2005 Cirrus Logic, Inc.

17

Version 2.3

5.0 Synchronization

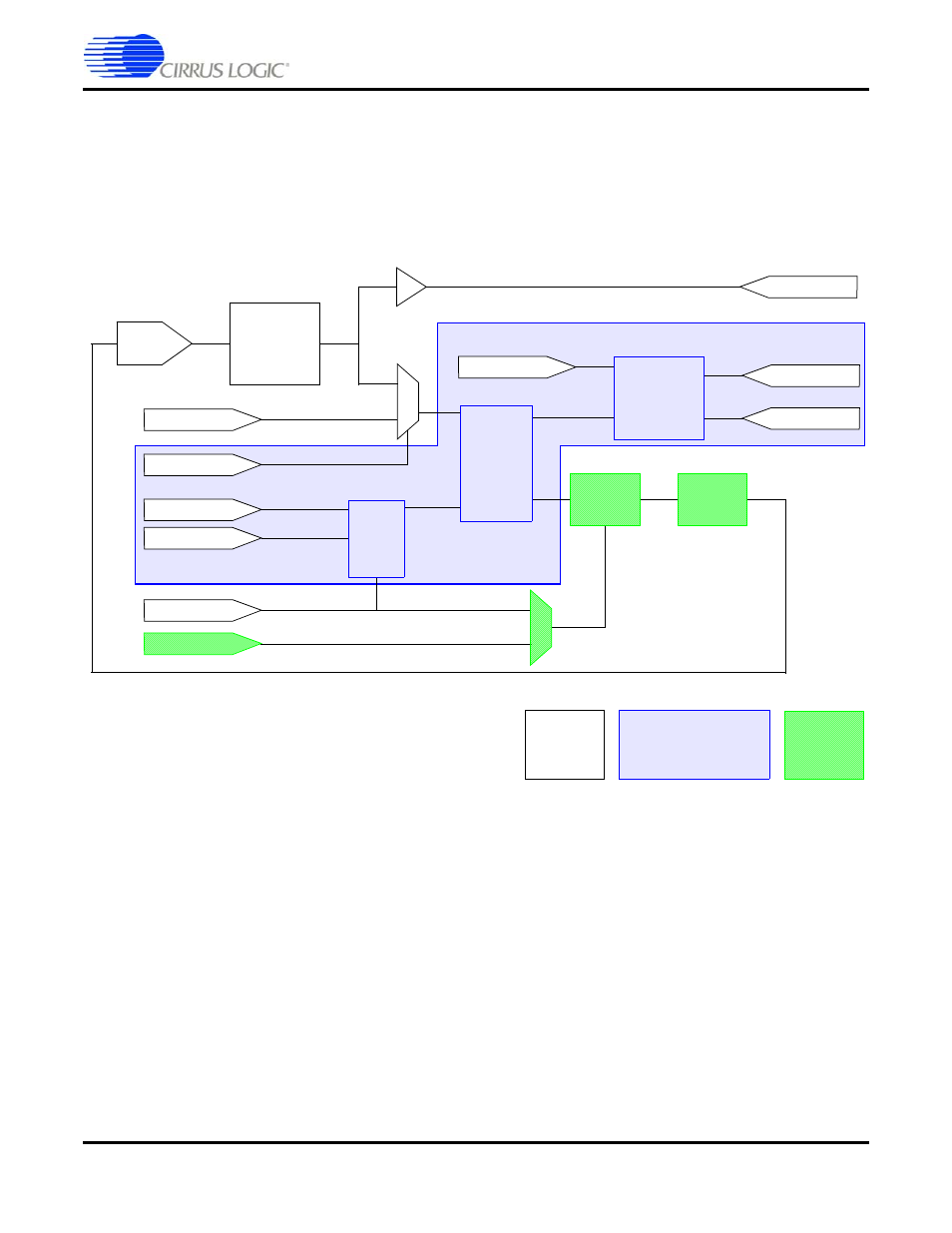

shows clock related circuits for the CS1810xx/CS4961xx and board design

(CM-2). This circuitry allows the synchronization modes documented below to be

achieved. Modes are distinguished by different settings of the multiplexors and software

elements.

Figure 3. Audio Clock Sub-system

5.1

Synchronization Modes

Clock synchronization mode for conductor and performer roles is independently

selectable via management interface variables

syncConductorClock and

syncPerformerClock. The role (conductor or performer) is determined by the network

environment including the

conductor priority setting of the device and the other devices on

the network. It is possible to ensure you will never assume the conductor role by selecting

a conductor priority of

zero. However, it is not reasonable to assume that by setting a high

conductor priority, you will always assume the conductor role. For more information, refer

to CobraNet Programmer’s Reference Manual.

VCXO

24.576 MHz

MCLK_OUT

MCLK_IN

MCLK_SEL

AClkConfig

RefClkEnable

RefClkPolarity

REFCLK_IN

Legend:

External

Software

Component

Hardware

Component

(CM2)

Internal

Hardware

Component

(CS1810xx, CS4961xx)

CS1810xx/CS4961xx

DAC

FS1

SLCK

Phase

Detector

Loop

Filter

Sample

Phase

Counter

Edge

Detect

Audio

Clock

Generator

BeatReceived