Cirrus Logic CS1810xx User Manual

Page 45

CobraNet Hardware User’s Manual

Mechanical Drawings and Schematics

DS651UM23

©

Copyright 2005 Cirrus Logic, Inc.

45

Version 2.3

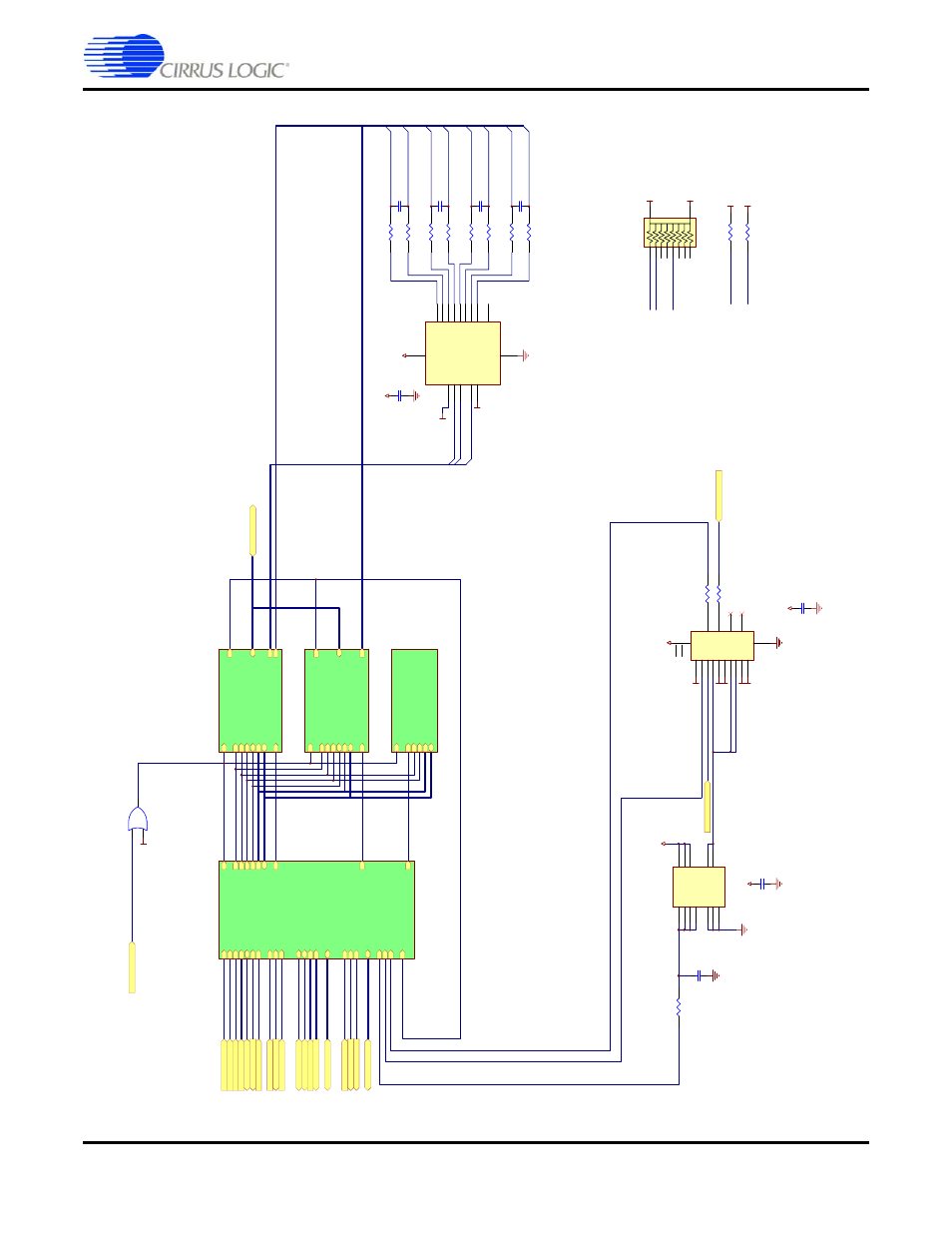

Figure 25. CM-2 RevF Schematic Page 2 of 7

CT

RL

B1

GN

D

AB

2

OUT

AB

3

VCC

B4

CT

RL

A1

CT

RL

C1

CT

RL

D1

GN

D

C2

GN

D

D2

OUT

CD3

VCC

A4

VCC

CD4

U3

24.

576 M

H

z VCXO

A/B

1

1A

2

1B

3

1Y

4

2A

5

2B

6

2Y

7

GND

8

3Y

9

3B

10

3A

11

4Y

12

4B

13

4A

14

G

15

VCC

16

U4

74L

VC157

MC

LK

_

S

E

L

GN

D

HRESET

_B

UF

#

M

AC_CS#

OE#

WE

#

IO

W

A

IT

ADDR[

0.

.19]

DAT

A[

0.

.15]

MA

C

_

IR

Q

0

MA

C

_

IR

Q

1

F

L

ASH_CS#

ADDR[0..19]

DATA[0..15]

AUX_POW

ER[

3

..

0

]

AUX_POW

ER[

3

..

0

]

U

A

R

T_

TX

_

O

E

UART

_RXD

U

A

R

T_

TX

D

HRW

HDS#

HEN#

HREQ#

HACK

#

HADDR[

0.

.3

]

HDAT

A[

0.

.7

]

FS

1

SSI

_CL

K

SSI

_DOUT

[0

..

3

]

S

S

I_

D

IN

[0

..3

]

G

P

IO

[0

..1

]

HEN#

HRW

HDS#

HADDR[

0.

.3

]

HDAT

A[

0.

.7

]

HREQ#

HACK

#

U

A

R

T_

TX

_

O

E

U

A

R

T_

TX

D

UART

_RXD

FS

1

SSI

_CL

K

S

S

I_

D

IN

[0

..3

]

SSI

_DOUT

[0

..

3

]

G

P

IO

[0

..1

]

HRESET

#

DAT

A[

0.

.15]

ADDR[

0.

.19]

HRESET

_B

UF

#

OE#

WE

#

F

L

ASH_CS#

fl

as

h

fl

as

h

.s

ch

REF

CL

K

_

IN

W

A

T

C

HDOG

MU

TE

#

REF

CL

K

_

IN

W

A

T

C

HDOG

MU

TE

#

R4

30.

9 Ohm

, 1%

R5

30.

9 Ohm

, 1%

C16

0.

1 uF

R6

30.

9 Ohm

, 1%

R7

30.

9 Ohm

, 1%

C17

0.

1 uF

R8

30.

9 Ohm

, 1%

R9

30.

9 Ohm

, 1%

C18

0.

1 uF

R10

30.

9 Ohm

, 1%

R11

30.

9 Ohm

, 1%

C20

0.

1 uF

L

E

D Filters

g

o

clos

e to the connector.

LE

D

_

BU

F

0

LE

D

_

BU

F

1

LE

D

_

BU

F

2

LE

D

_

BU

F

3

LE

D

_

BU

F

4

LE

D

_

BU

F

5

LE

D

_

BU

F

6

LE

D

_

BU

F

7

LED_BUF[0..7]

LED_CTRL[0..2]

L

E

D_CT

RL

0

L

E

D_CT

RL

1

L

E

D_CT

RL

2

GN

D

VCC_+

3.

3

VCC_+

3.

3

L

E

D

_

C

T

R

L

[0

..2

]

L

E

D

_

B

U

F

[0

..7

]

L

E

D

_

B

U

F

[0

..7

]

MC

LK

_

IN

VCXO_OUT

VCXO_OUT

VCXO_OUT

GN

D

GN

D

GN

D

GN

D

M

C

L

K

_I

NT

ERNAL

M

C

L

K

_OUT

R16

2

4

.9

O

h

m

, 1

%

VCC_+

3.

3

C19

0.

1 uF

R12

3.

3K

Ohm

VCXO_CT

RL

MC

LK

_

IN

VCXO_CT

RL

MC

LK

_

S

E

L

M

C

L

K

_I

NT

ERNAL

M

C

L

K

_OUT

C21

0.

1 uF

VCC_+

3.

3

C22

0.

1 uF

VCC_+

3.

3

C15

0.

1 uF

VCC_+

3.

3

VCC_+

3.

3

ADDR[

0.

.19]

DAT

A[

0.

.15]

AUX_POW

ER[

0

..

3

]

HRESET

_B

UF

#

OE#

WE

#

M

AC_CS#

IO

W

A

IT

MA

C

_

IR

Q

0

L

E

D

_

C

T

R

L

[0

..2

]

L

E

D

_

B

U

F

[0

..7

]

CL

K

_25

m

acphy

1

m

acphy

1.

sch

ADDR[

0.

.19]

DAT

A[

0.

.15]

AUX_POW

ER[

0

..

3

]

HRESET

_B

UF

#

OE#

WE

#

M

AC_CS#

IO

W

A

IT

MA

C

_

IR

Q

1

L

E

D

_

B

U

F

[0

..7

]

CL

K

_25

m

acphy

2

m

acphy

2.

sch

CL

K

_25

CL

K

_25

CL

K

_25

R44

24.

9

Ohm

, 1%

Q1

1

Q2

2

Q3

3

Q4

4

Q5

5

Q6

6

Q7

7

GND

8

CASCADE

9

SCL

R#

10

SCK

11

RCK

12

OE#

13

DI

N

14

Q0

15

VCC

16

U2

74L

V595

R3

10K

Ohm

GN

D

W

A

T

C

HDOG

MU

TE

#

MC

LK

_

S

E

L

VCXO_CT

RL

R15

3.

3K

Ohm

GN

D

IO

W

A

IT

VCC_+

3.

3

VCC_+

3.

3

1

2

3

4

5

6

7

8

9

10

RN2

10K

Ohm

, 8x Array

4

5

6

U10B

74L

VC32

GN

D

HRESET

#

RSVD[

1.

.5

]

RSVD[

1.

.5

]

DAT

A[

0.

.15]

ADDR[

0.

.19]

HRESET

_B

UF

#

OE#

WE

#

F

L

ASH_CS#

M

AC_CS#

IO

W

A

IT

U

A

R

T_

TX

_

O

E

UART

_RXD

U

A

R

T_

TX

D

HRW

HDS#

HEN#

HREQ#

HACK

#

HADDR[

0.

.3

]

HDAT

A[

0.

.7

]

M

C

L

K

_I

NT

ERNAL

FS

1

SSI

_CL

K

SSI

_DOUT

[0

..

3

]

S

S

I_

D

IN

[0

..3

]

MC

LK

_

S

E

L

VCXO_CT

RL

MA

C

_

IR

Q

0

MA

C

_

IR

Q

1

G

P

IO

[0

..1

]

REF

CL

K

_

IN

W

A

T

C

HDOG

MU

TE

#

CL

K

_25

RSVD[

1.

.5

]

dsp

dsp.

sch