0 host management interface (hmi), 1 hardware – Cirrus Logic CS1810xx User Manual

Page 23

CobraNet Hardware User’s Manual

Host Management Interface (HMI)

DS651UM23

©

Copyright 2005 Cirrus Logic, Inc.

23

Version 2.3

7.0 Host Management Interface (HMI)

7.1

Hardware

The host port is 8 bits wide with 4 bits of addressing. Ten of the 16 addressable registers

are implemented. The upper two registers can be used to configure and retrieve the

status on the host port hardware. However, only the first 8 are essential for normal HMI

communications. It is therefore feasible, in most applications, to utilize only the first 3

address bits and tie the most significant bit (A3) low.

Host port hardware supports Intel

®

(little-endian), Motorola

®

, and Motorola multiplexed

bus

(big-endian) protocols. Standard CobraNet firmware configures the port in the

Motorola,

big-endian mode.

The host port memory map is shown in

. Refer also to

and

.

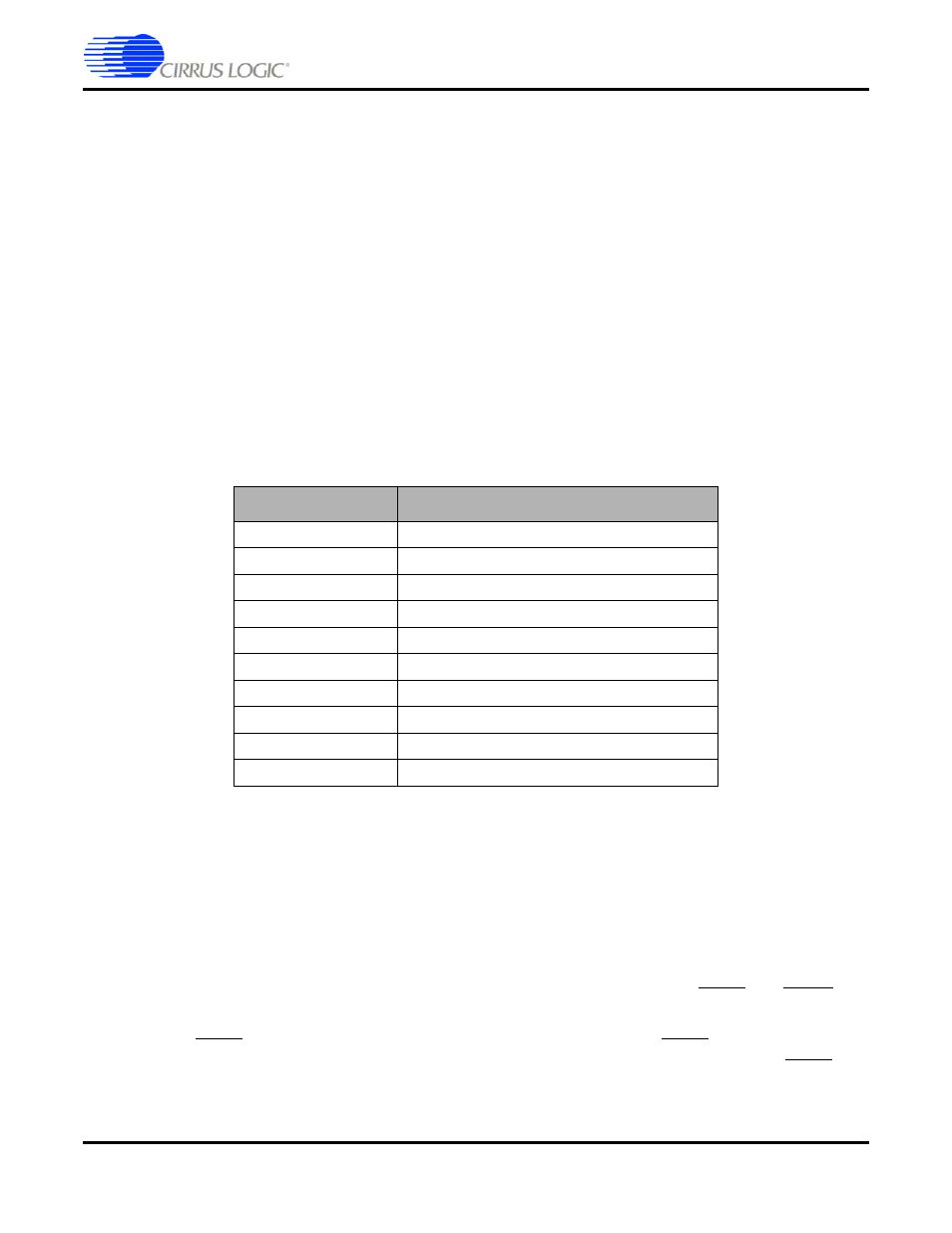

Table 3. Host port memory map

The message and data registers provide separate bi-directional data conduits between

the host processor and the CS1810xx/CS4961xx. A 32-bit word of data is transferred to

the CS1810xx/CS4961xx when the host writes the D message or data register after

presumably previously writing the A, B, and C registers with valid data. Data is transferred

from the CS1810xx/CS4961xx following a read of the D message or data register. Again,

presumably the A, B, and C registers are read previously.

Two additional hardware signals are associated with the host port: HACK and HREQ.

Both are outputs to the host.

HACK may be wired to an interrupt request input on the host. HACK can be made to

assert (logic 0) on specific events as specified by the

hackEnable MI variable. HACK is

deasserted (logic 1) by issuance of the

Acknowledge Interrupt message (see “Messages”

below).

Host Address

Register

0

Message A (MS)

1

Message B

2

Message C

3

Message D (LS)

4

Data A (MS)

5

Data B

6

Data C

7

Data D (LS)

8

Control

9

Status