3 chipset chipset chipset chipset chipset, Ecc redirection [disabled, Dram background scrubber [disabled – Asus TW510-E2 User Manual

Page 104: L2 cache background scrubber [disabled, Dcache background scrubber [disabled, Onchip ide channel0 [enabled, Onchip ide channel1 [enabled

5 - 2 4

5 - 2 4

5 - 2 4

5 - 2 4

5 - 2 4

C h a p t e r 5 : B I O S s e t u p

C h a p t e r 5 : B I O S s e t u p

C h a p t e r 5 : B I O S s e t u p

C h a p t e r 5 : B I O S s e t u p

C h a p t e r 5 : B I O S s e t u p

ECC Redirection [Disabled]

ECC Redirection [Disabled]

ECC Redirection [Disabled]

ECC Redirection [Disabled]

ECC Redirection [Disabled]

When set to [Enabled], correctable errors are corrected as the data is

passed to the requestor. The data in the DRAM is not corrected if this item

is set to [Disabled]. Configuration options: [Disabled] [Enabled]

DRAM Background Scrubber [Disabled]

DRAM Background Scrubber [Disabled]

DRAM Background Scrubber [Disabled]

DRAM Background Scrubber [Disabled]

DRAM Background Scrubber [Disabled]

Specifies the scrub rate of the next address to be scrubbed by the DRAM

scrubber. Configuration options: [Disabled] [40.0ns]

L2 Cache Background Scrubber [Disabled]

L2 Cache Background Scrubber [Disabled]

L2 Cache Background Scrubber [Disabled]

L2 Cache Background Scrubber [Disabled]

L2 Cache Background Scrubber [Disabled]

Specifies the scrub rate of the next address to be scrubbed by the L2

cache scrubber. Configuration options: [Disabled] [40.0ns]

DCache Background Scrubber [Disabled]

DCache Background Scrubber [Disabled]

DCache Background Scrubber [Disabled]

DCache Background Scrubber [Disabled]

DCache Background Scrubber [Disabled]

Specifies the scrub rate of the next address to be scrubbed by the data

cache scrubber. Configuration options: [Disabled] [40.0ns]

5.4.3

5.4.3

5.4.3

5.4.3

5.4.3

Chipset

Chipset

Chipset

Chipset

Chipset

This menu shows the chipset configuration settings. Select an item then

press

OnChip IDE Channel0 [Enabled]

OnChip IDE Channel0 [Enabled]

OnChip IDE Channel0 [Enabled]

OnChip IDE Channel0 [Enabled]

OnChip IDE Channel0 [Enabled]

Enables or disables the on-chip IDE channel 0. Configuration options:

[Disabled] [Enabled]

OnChip IDE Channel1 [Enabled]

OnChip IDE Channel1 [Enabled]

OnChip IDE Channel1 [Enabled]

OnChip IDE Channel1 [Enabled]

OnChip IDE Channel1 [Enabled]

Enables or disables the on-chip IDE channel 1. Configuration options:

[Disabled] [Enabled]

F1:Help

↑↓

↑↓

↑↓

↑↓

↑↓ : Select Item

-/+: Change Value

F5: Setup Defaults

ESC: Exit

→←

→←

→←

→←

→←: Select Menu

Enter: Select Sub-menu

F10: Save and Exit

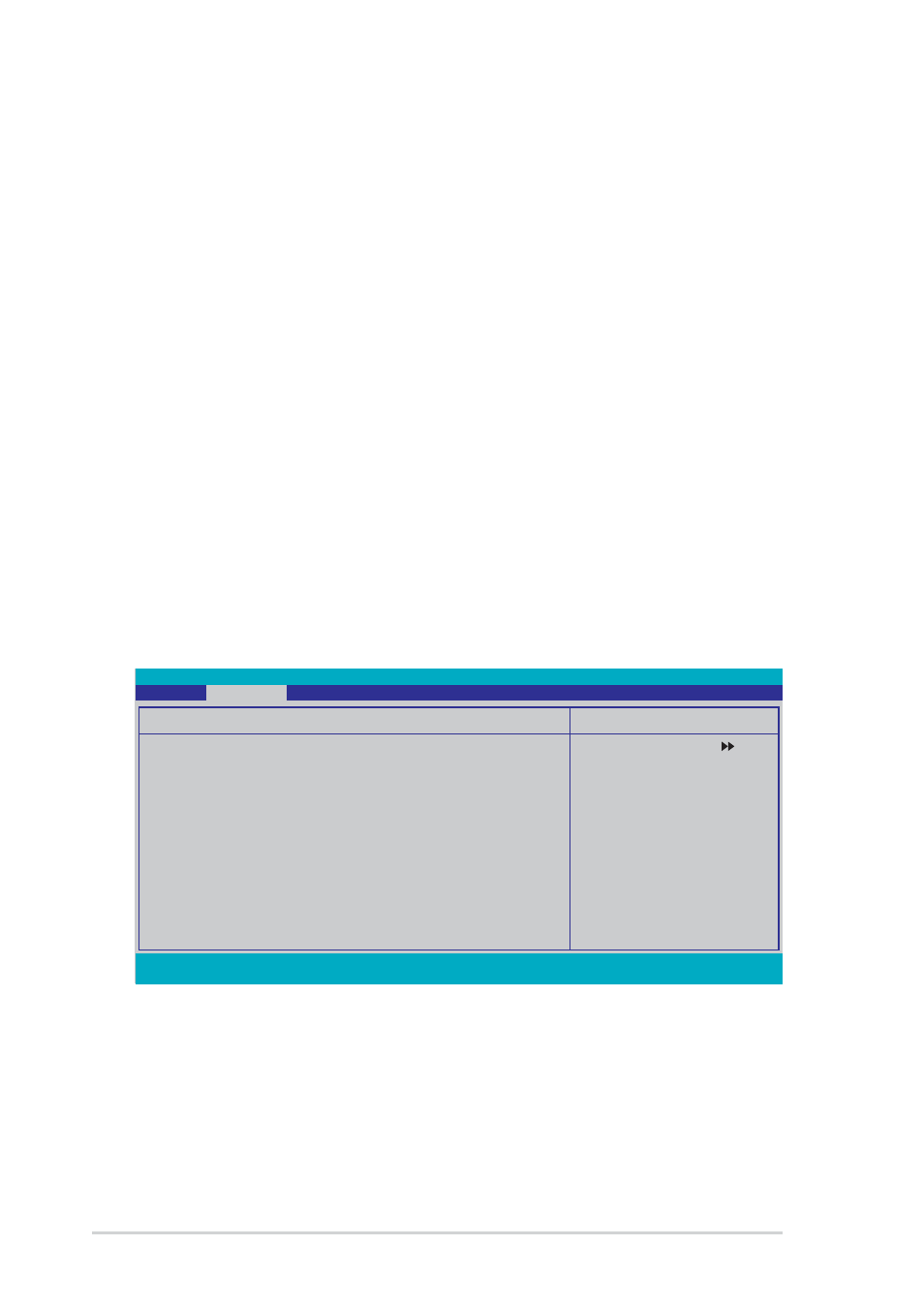

Phoenix-Award BIOS CMOS Setup Utility

Advanced

Select Menu

Item Specific Help

Disable/Enable OnChip IDE

Channel0.

Chipset

OnChip IDE Channel0

[Enabled]

OnChip IDE Channel1

[Enabled]

Hyper Transport Frequency

[4x]

Hyper Transport Width

[

↓

↓

↓

↓

↓16 ↑

↑

↑

↑

↑16]

Errata 94 Enhanced

[Auto]

System BIOS Cacheable

[Disabled]

Spread Spectrum

[Enabled]

SATA Spread Spectrum

[Disabled]

PCIE Spread Spectrum

[Disabled]

SSE/SSE2 Instructions

[Enabled]

Init Display First

[PCI Slot]

IDE DMA Transfer Access

[Enabled]

Serial-ATA 1

[Enabled]

SATA DMA Transfer

[Enabled]

Serial-ATA 2

[Enabled]

SATA2 DMA Transfer

[Enabled]

IDE Prefetch Mode

[Enabled]