Table 31. tmr_config (address = 21h), Table 30. tmr_control (address = 20h) – Rainbow Electronics MAX1464 User Manual

Page 38

MAX1464

Low-Power, Low-Noise Multichannel

Sensor Signal Processor

38

______________________________________________________________________________________

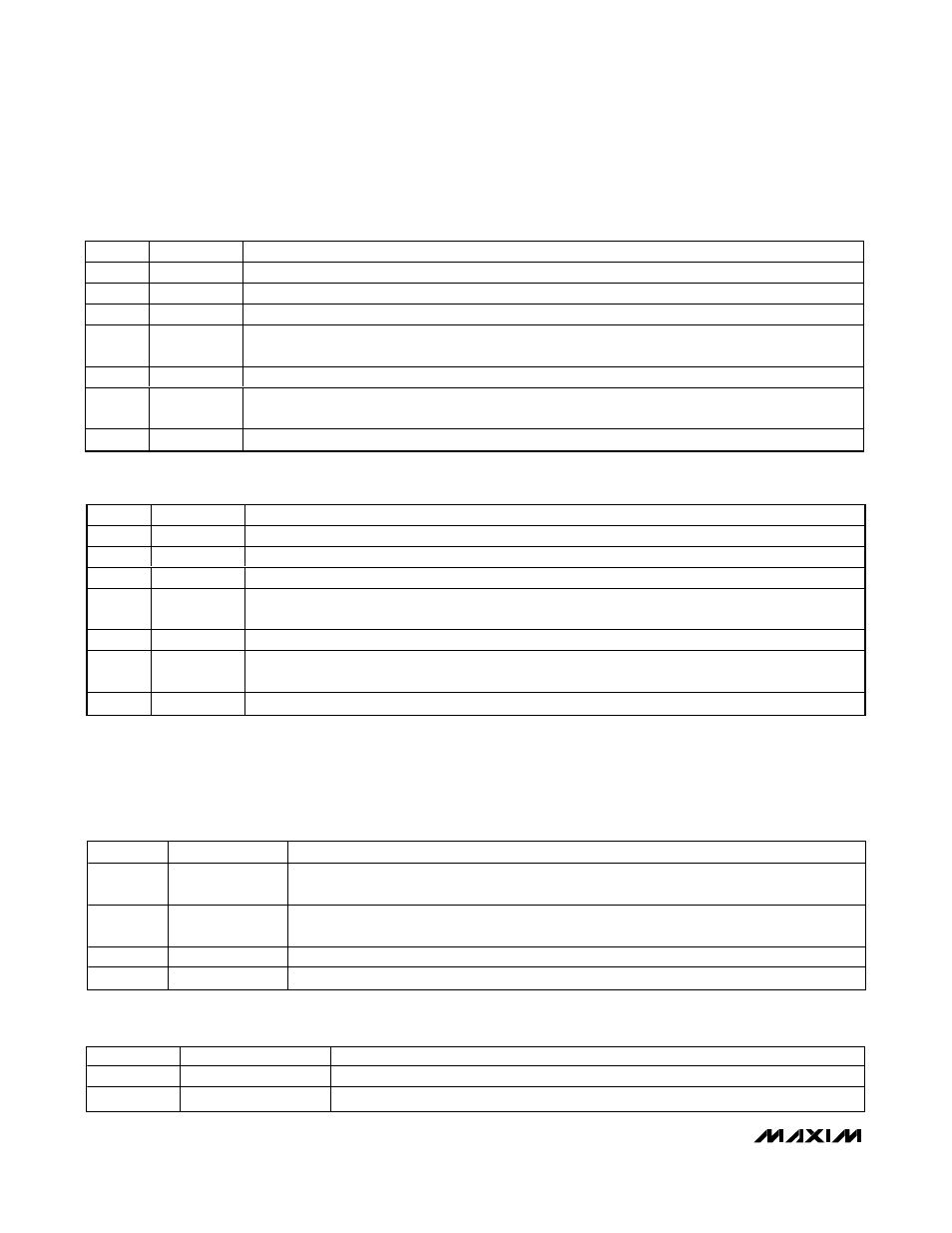

BIT

NAME

DESCRIPTION

15–12

PS[3:0]

Prescaler setting to use during the timing interval. PS[3 ] = MSB.

11–0

TO[11:0]

Timeout value to use during the timing interval. TO[11] = MSB.

Table 31. TMR_Config (Address = 21h)

BITS

NAME

DESCRIPTION

15–6

—

Unused.

5

OUT2

OUT2 value is driven onto the GPIO2 pin when the output driver is enabled.

4

EN2

Enable the output driver; 1 = enabled, 0 = disabled, and OUT tri-stated.

3

IN2

When EDGE2 = 0: The value input on GPIO2 is clocked into this bit (Notes 14, 15).

When EDGE2 = 1: An edge detection on GPIO2 causes a 1 to be clocked into this bit.

2

CLR2

Clear IN2 bit; 1 = clear IN2 to 0, 0 = IN2 retains its status (Note 16).

1

INV2

When EDGE2 = 0: Invert the logic value IN2; 1 = invert input, 0 = do not invert. When EDGE2 = 1: Select

edge capture type; 1 = falling edge detect; 0 = rising edge detect.

0

EDGE2

Select level or edge detection at IN2; 1 = detect edges, 0 = detect and track logic levels.

Table 29. GPIO2_Control (Address = 41h)

Note 14: A pulse or level must remain on GPIOn for four periods of f

OSC

to be latched into IN.

Note 15: The CLRn bit must be cleared to zero to reenable GPIO to value tracking.

Note 16: The CLRn bit must be cleared to zero to reenable GPIO edge detection.

BIT

NAME

DESCRIPTION

15

TMDN

Timer done bit set by the counter; 1 = timeout value reached, 0 = timeout not reached. Read-only

bit.

14

TMEN

Timer enable bit; A 1 written to TMEN resets TMDN to zero and starts counter. TMEN is reset to

zero by the counter when timeout value is reached.

13–1

—

Unused.

0

ENAHALT

Enable CPU halt; 1 = CPU halted for duration of timer interval, 0 = CPU not halted.

Table 30. TMR_Control (Address = 20h)

BITS

NAME

DESCRIPTION

15–6

—

Unused.

5

OUT1

OUT1 value is driven onto the GPIO1 pin when the output driver is enabled.

4

EN1

Enable the output driver; 1 = enabled, 0 = disabled, and OUT tri-stated.

3

IN1

When EDGE1 = 0: The value input on GPIO1 is clocked into this bit (Notes 14, 15).

When EDGE1 = 1: An edge detection on GPIO1 causes a 1 to be clocked into this bit.

2

CLR1

Clear IN1 bit; 1 = clear IN1 to 0, 0 = IN1 retains its status (Note 16).

1

INV1

When EDGE1 = 0: Invert the logic value IN1; 1 = invert input, 0 = do not invert. When EDGE1 = 1: Select

edge capture type; 1 = falling edge detect; 0 = rising edge detect.

0

EDGE1

Select level or edge detection at IN1; 1 = detect edges, 0 = detect and track logic levels.

Table 28. GPIO1_Control (Address = 40h)