Rainbow Electronics DS2188 User Manual

Page 5

DS2188

021997 5/11

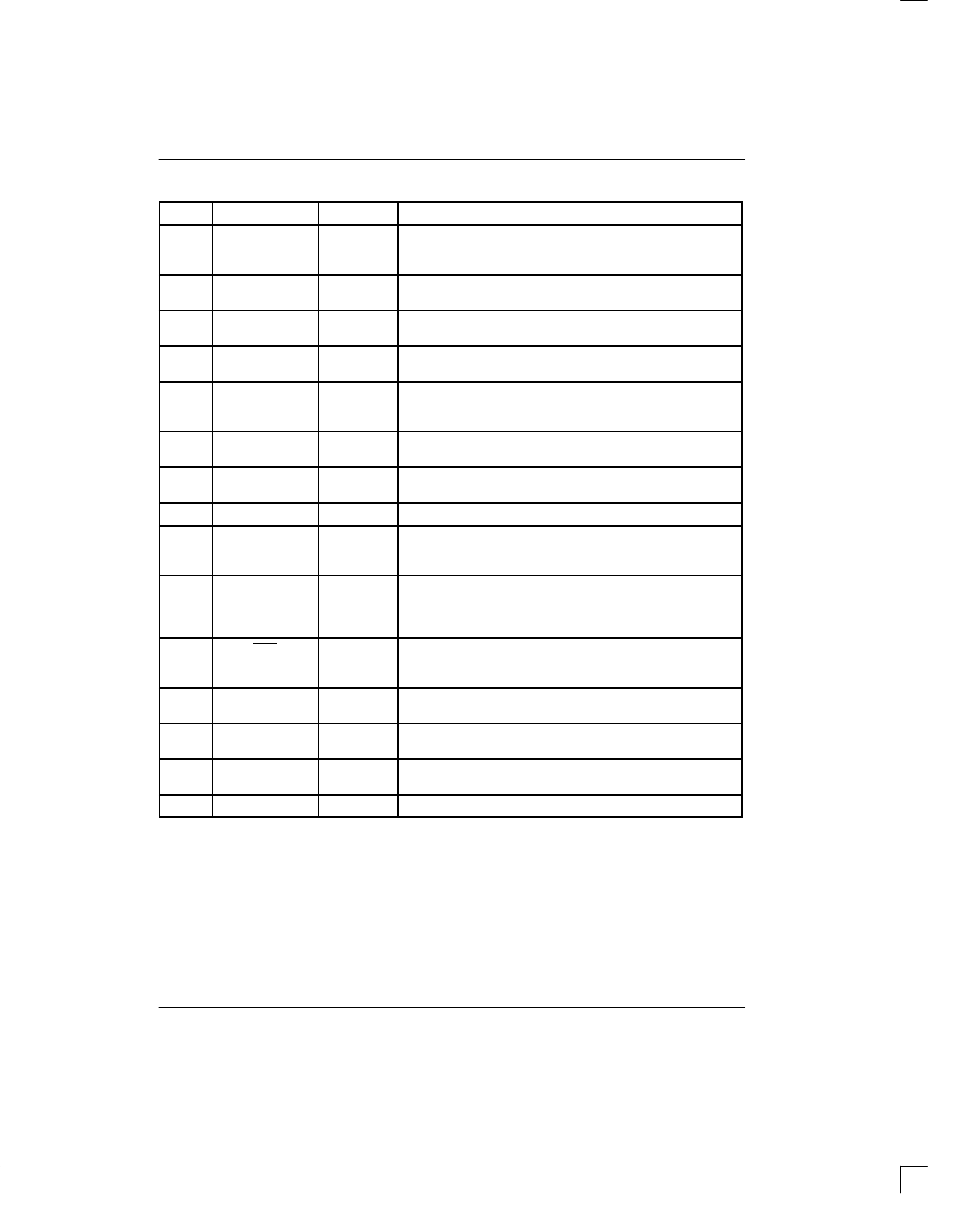

PIN DESCRIPTION Table 1

PIN

SYMBOL

TYPE

DESCRIPTION

1

DJA

I

Disable Jitter Attenuation. When high, jittered data and clock

at RPOS, RNEG, and RCLK are passed directly to RRPOS,

RRNEG, and RRCLK.

2

RPOS

I

Receive Positive Data Input. Jittered data input. Sampled on

the falling edge of RCLK.

3

RNEG

I

Receive Negative Data Input. Jittered data input. Sampled on

the falling edge of RCLK.

4

RCLK

I

Receive Clock Input. Jittered input 1.544 MHz or 2.048 MHz

clock.

5

BDS

I

Buffer Depth Select.

0 = 128 bits

1 = 32 bits

6

TEST

I

Test Input. In normal applications, this pin should be tied low.

When tied high, used to verify free running frequency of XTAL.

7

XTAL OUT

O

Crystal Frequency Output. Buffered output of the 4X crystal

connected to XTAL1 and XTAL2.

8

V

SS

–

Ground. 0.0 volts.

9

10

XTAL1

XTAL2

I

O

Crystal Connections. In T1 environments, connect a 6.176

MHz crystal to these pins. In CEPT environments, connect a

8.192 MHz crystal to these pins.

11

BL

O

Buffer Limit. Transitions high when the buffer fills or empties to

within either 4 bits (BDS=0) or 2 bits (BDS=1) of its capacity.

Indicates that the jitter at RCLK is greater than 120UIpp

(BDS=0) or 28UIpp (BDS=1).

12

RST

I

Reset. Negative–edge triggered; a high–low transition will re-

center the buffer. Activation of this pin may corrupt data through

the DS2188.

13

RRCLK

O

Receive Reference Clock. Dejittered 1.544 MHz or 2.048 MHz

clock.

14

RRNEG

O

Receive Reference Negative Data Output. Dejittered data

output. Updated on the rising edge of RRCLK.

15

RRPOS

O

Receive Reference Positive Data Output. Dejittered data

output. Updated on the rising edge of RRCLK.

16

V

DD

–

Positive Supply. 5.0 volts.