Rainbow Electronics AT90S8515 User Manual

Page 39

39

AT90S8515

0841G–09/01

Timer/Counter1 Output

Compare Register – OCR1BH

AND OCR1BL

The output compare registers are 16-bit read/write registers.

The Timer/Counter1 Output Compare registers contain the data to be continuously com-

pared with Timer/Counter1. Actions on compare matches are specified in the

Timer/Counter1 Control and Status registers. A compare match only occurs if

Timer/Counter1 counts to the OCR value. A software write that sets TCNT1 and OCR1A

or OCR1B to the same value does not generate a compare match.

A compare match will set the compare interrupt flag in the CPU clock cycle following the

compare event.

Since the Output Compare Registers (OCR1A and OCR1B) are 16-bit registers, a tem-

porary register (TEMP) is used when OCR1A/B are written to ensure that both bytes are

updated simultaneously. When the CPU writes the high byte, OCR1AH or OCR1BH, the

data is temporarily stored in the TEMP register. When the CPU writes the low byte,

OCR1AL or OCR1BL, the TEMP register is simultaneously written to OCR1AH or

OCR1BH. Consequently, the high byte OCR1AH or OCR1BH must be written first for a

full 16-bit register write operation.

The TEMP register is also used when accessing TCNT1 and ICR1. If the main program

and interrupt routines perform access to registers using TEMP, interrupts must be dis-

abled during access from the main program (and from interrupt routines if interrupts are

allowed from within interrupt routines).

Timer/Counter1 Input Capture

Register – ICR1H AND ICR1L

The input capture register is a 16-bit read-only register.

When the rising or falling edge (according to the input capture edge setting [ICES1]) of

the signal at the input capture pin (ICP) is detected, the current value of the

Timer/Counter1 is transferred to the Input Capture Register (ICR1). At the same time,

the input capture flag (ICF1) is set (one).

Since the Input Capture Register (ICR1) is a 16-bit register, a temporary register

(TEMP) is used when ICR1 is read to ensure that both bytes are read simultaneously.

When the CPU reads the low byte ICR1L, the data is sent to the CPU and the data of

the high byte ICR1H is placed in the TEMP register. When the CPU reads the data in

the high byte ICR1H, the CPU receives the data in the TEMP register. Consequently,

the low byte ICR1L must be accessed first for a full 16-bit register read operation.

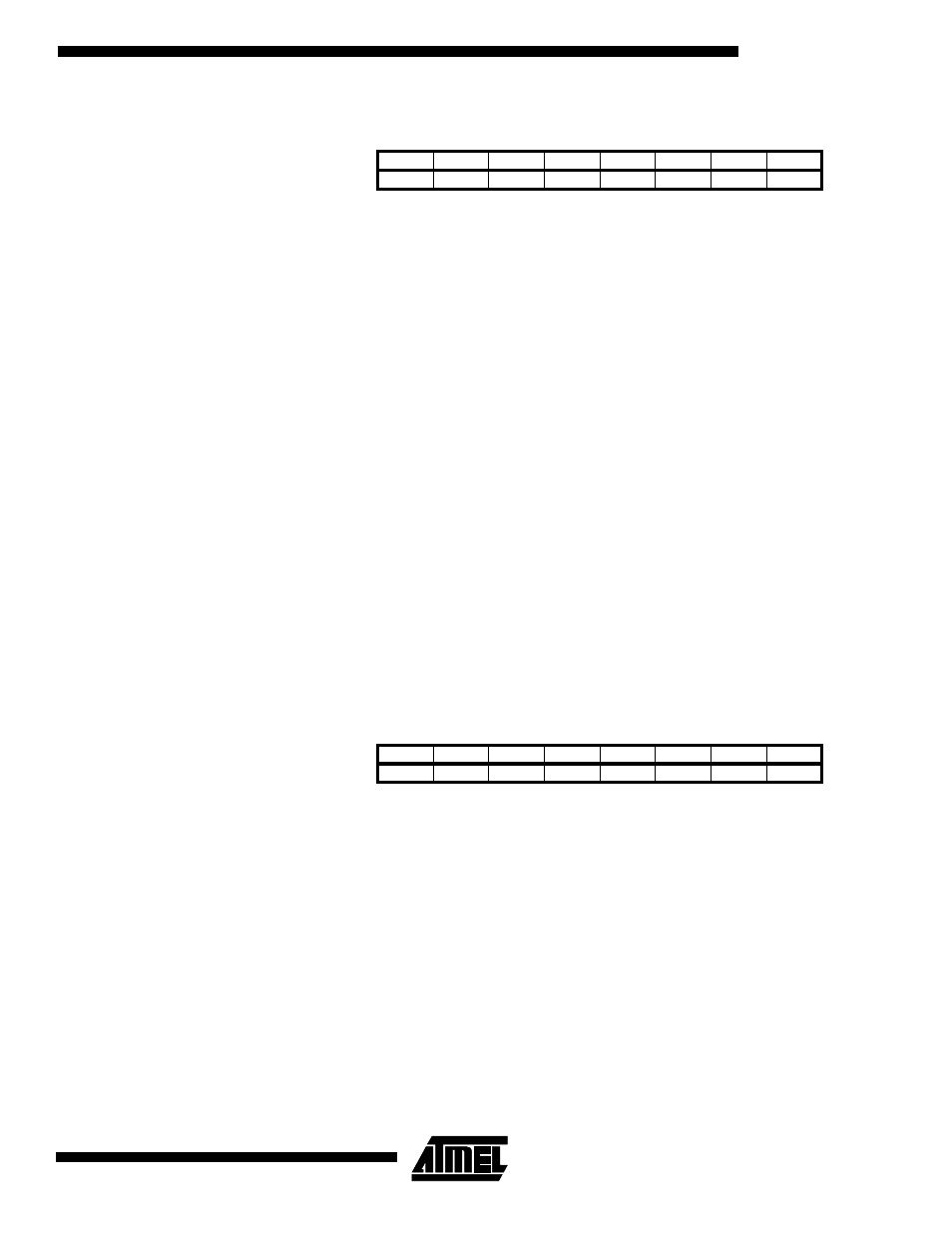

Bit

15

14

13

12

11

10

9

8

$29 ($49)

MSB

OCR1BH

$28 ($48)

LSB

OCR1BL

7

6

5

4

3

2

1

0

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

$25 ($45)

MSB

ICR1H

$24 ($44)

LSB

ICR1L

7

6

5

4

3

2

1

0

Read/Write

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Initial Value

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0