Table 56. ramp register (slope setting for buck1) – Rainbow Electronics MAX8982X User Manual

Page 67

Power-Management ICs for

ICERA E400/E450 Platform

MAX8982A/MAX8982X

67

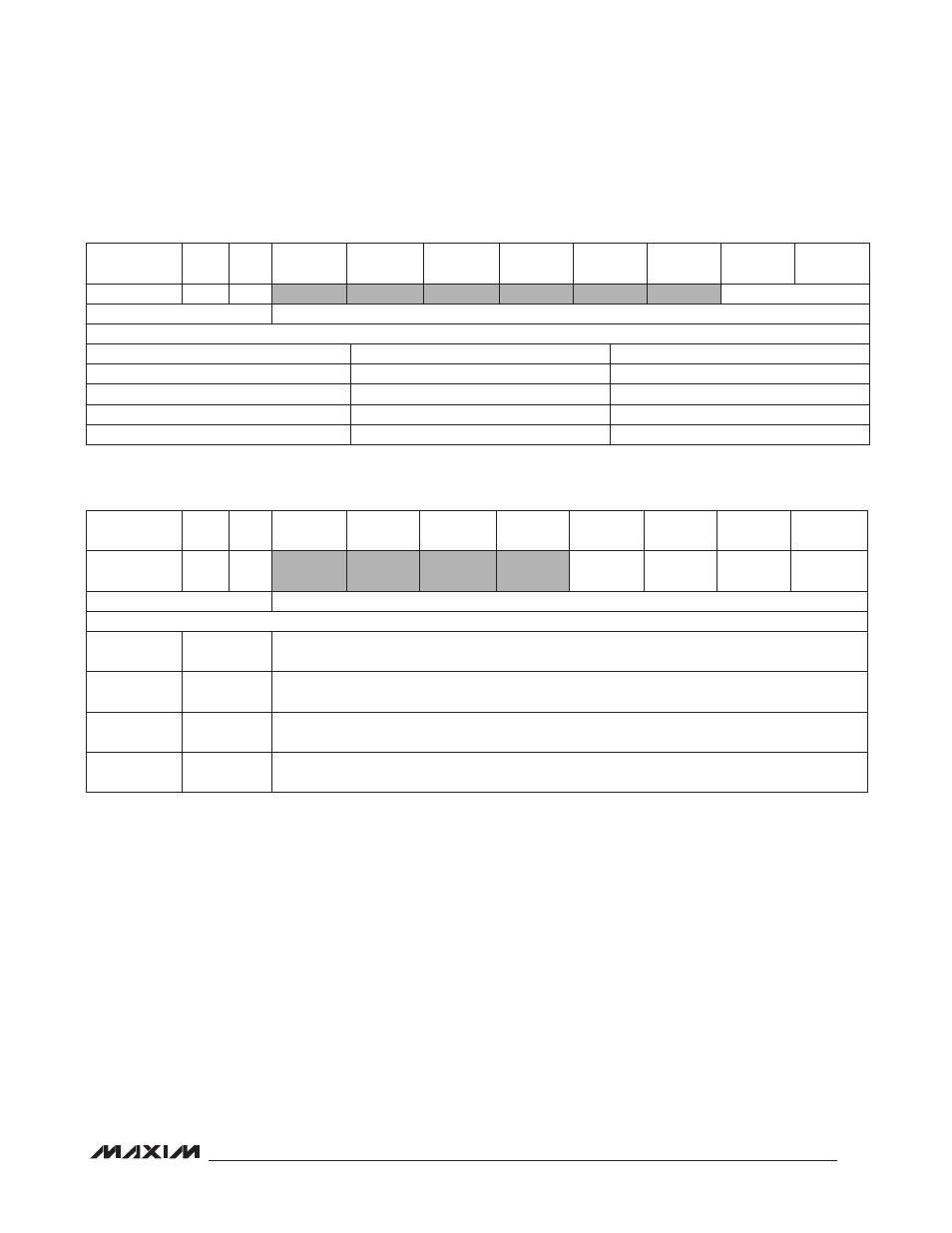

Table 56. RAMP Register (Slope Setting for BUCK1)

Table 57. BUCK1-4ADIS Register (Active Discharge Settings for BUCK1–BUCK4)

Note: The SD3ADIS and SD4ADIS bits are not used by the MAX8982X.

ADDRESS

(HEX)

POR

(HEX)

R/W

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

77

02

R/W

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

RASD1[1:0]

BITS 7:2

Reserved, write 000000 to these bits.

DESCRIPTION

BIT 1

BIT 0

SLEW RATE

(mV/µs)

0

0

5

0

1

10

1

0

12.5

1

1

25

ADDRESS

(HEX)

POR

(HEX)

R/W

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

78

04

R/W

Reserved

Reserved

Reserved

Reserved

SD1

ADIS

SD2

ADIS

SD3

ADIS

SD4

ADIS

BITS 7:4

Reserved, write 0000 to these bits.

DESCRIPTION

SD1ADIS

0

1: Enable BUCK1 active discharge.

0: Disable BUCK1 active discharge.

SD2ADIS

1

1: Enable BUCK2 active discharge.

0: Disable BUCK2 active discharge.

SD3ADIS

0

1: Enable BUCK3 active discharge.

0: Disable BUCK3 active discharge.

SD4ADIS

0

1: Enable BUCK4 active discharge.

0: Disable BUCK4 active discharge.