Table 6. chipid register, Table 7. irqm register (interrupt mask) – Rainbow Electronics MAX8982X User Manual

Page 45

Power-Management ICs for

ICERA E400/E450 Platform

MAX8982A/MAX8982X

45

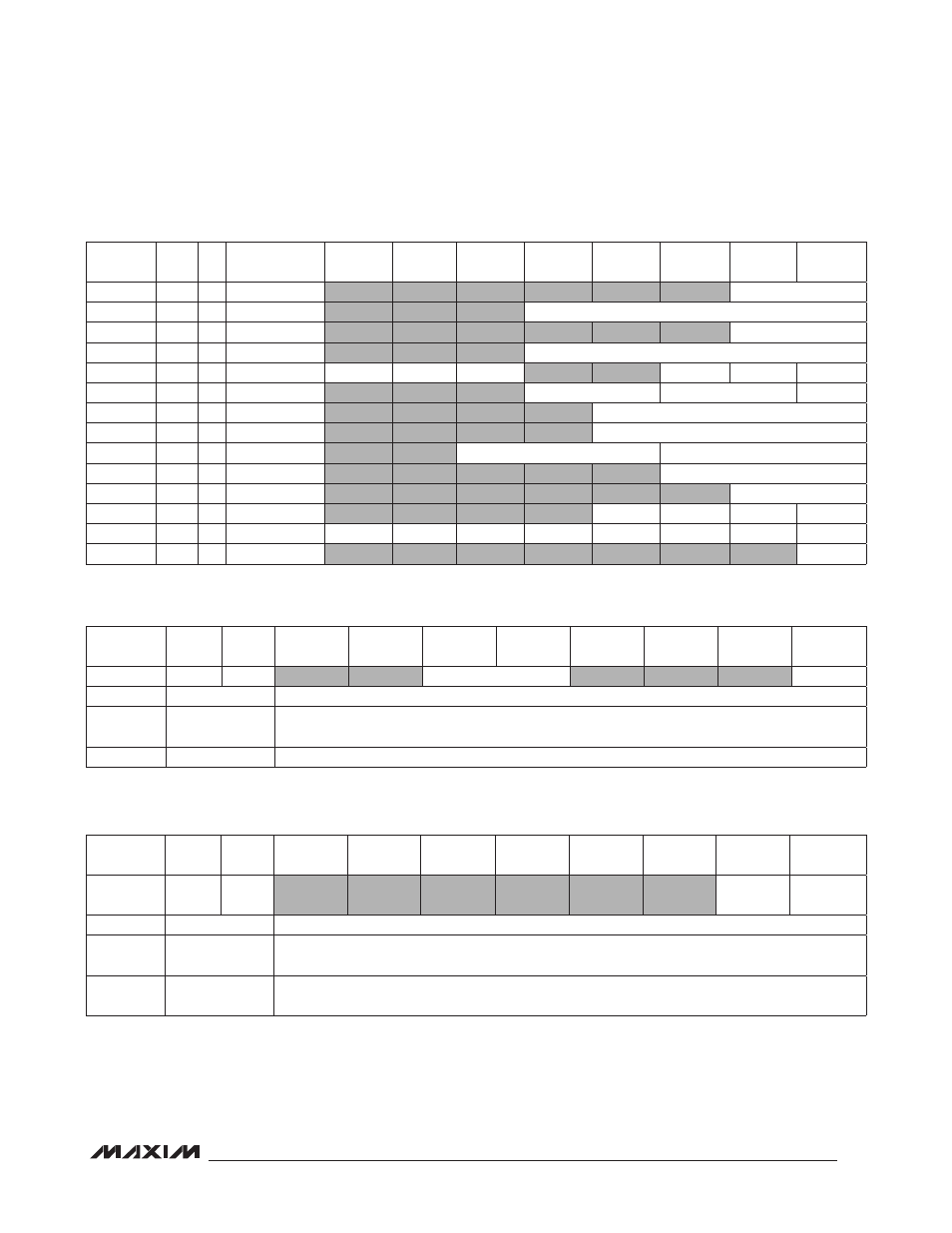

Table 6. CHIPID Register

Table 7. IRQM Register (Interrupt Mask)

Table 5. Register Map (continued)

Note: The IRQM register is effective only as long as IN1A and IN1B are higher than the falling UVLO threshold. If the IN1A and

IN1B are below the falling UVLO threshold, this IRQM register resets to the POR value.

ADDRESS

(HEX)

POR

(HEX)

R/W

NAME

BIT 7

(MSB)

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

(LSB)

5A

01 R/W

LDO8

Reserved Reserved Reserved Reserved Reserved Reserved

LDO8[1:0]

5B

06 R/W

LDO8V

Reserved Reserved Reserved

L8[4:0]

5C

01 R/W

LDO9

Reserved Reserved Reserved Reserved Reserved Reserved

LDO9[1:0]

5D

00 R/W

LDO9V

Reserved Reserved Reserved

L9[4:0]

6B

00 R/W

LED_EN

Reserved Reserved Reserved Reserved Reserved LED3EN

LED2EN

LED1EN

70

03 R/W

ON/OFF

Reserved Reserved Reserved

BUCK4[1:0]

BUCK3[1:0]

32KCLK

72

06 R/W

BUCK3

Reserved Reserved Reserved Reserved

SD3[3:0]

73

08 R/W

BUCK4

Reserved Reserved Reserved Reserved

SD4[3:0]

75

3F R/W CURRENTREG1 Reserved Reserved

DR1[2:0]

DR2[2:0]

76

07 R/W CURRENTREG2 Reserved Reserved Reserved Reserved Reserved

DR3[2:0]

77

02 R/W

RAMP

Reserved Reserved Reserved Reserved Reserved Reserved

RASD1[1:0]

78

04 R/W BUCK1-4ADIS Reserved Reserved Reserved Reserved SD1ADIS SD2ADIS SD3ADIS SD4ADIS

79

00 R/W LDO1-8ADIS LDO1ADIS LDO2ADIS LDO3ADIS LDO4ADIS LDO5ADIS LDO6ADIS LDO7ADIS LDO8ADIS

7A

00 R/W

LDO9ADIS

Reserved Reserved Reserved Reserved Reserved Reserved Reserved LDO9ADIS

ADDRESS

(HEX)

POR

(HEX)

R/W

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

02

—

R

Reserved

Reserved

PASS[1:0]

Reserved

Reserved

Reserved

VOPTION

NAME

POR

DESCRIPTION

VOPTION

—

0: 5V input option (MAX8982A)

1: 3.3V input option (MAX8982X)

PASS[1:0]

—

Chip revision version

ADDRESS

(HEX)

POR

(HEX)

R/W

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

03

00

R/W

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

UVLOFM

HIGH

TMPM

NAME

POR

DESCRIPTION

HIGH

TMPM

0

0: Interrupt enabled.

1: Mask HIGHTMP interrupt.

UVLOFM

0

0: Interrupt enabled.

1: Mask UVLOF interrupt.