Other spi flash control signals, Variant select pins, vs[2:0, Jumper block j11 – Xilinx MIcroblaze Development Spartan-3E 1600E User Manual

Page 104: Programming header j12, Multi-package layout

102

MicroBlaze Development Kit Spartan-3E 1600 Edition User Guide

UG257 (v1.1) December 5, 2007

Chapter 12:

SPI Serial Flash

R

Other SPI Flash Control Signals

The M25P16 SPI Flash has two additional control inputs. The active-Low write protect

input (W) and the active-Low bus hold input (HLD) are unused and pulled High via an

external pull-up resistor.

Variant Select Pins, VS[2:0]

When in SPI configuration mode, the FPGA samples the value on three pins, labeled

VS[2:0], to determine which SPI read command to issue to the SPI Flash. For the M25P16

Flash, VS[2:0]=<1:1:1> issues the correct command sequence. The VS[2:0] pins are pulled

High externally via pull-up resistors to 3.3V. The VS[2:0] pins are also parallel NOR Flash

address lines A[19:17] in the FPGA’s BPI configuration mode and these signals also

connect to the StrataFlash parallel Flash PROM. After SPI configuration, the VS[2:0] pins

become user-programmable I/O pins, allowing full access to the StrataFlash PROM,

despite that the FPGA configured from SPI Flash.

Jumper Block J11

In SPI configuration mode, the FPGA selects the attached SPI Flash by asserting the CSO_B

pin Low. On the MicroBlaze Development Kit board, the CSO_B pin drives into the jumper

J11 block. This jumper block provides the option to move the on-board SPI Flash to a

different select line (SPI_ALT_CS_JP11). This way, a different SPI Flash device can be tested

by changing the JP11 jumper settings and connecting the alternate SPI Flash on Header

JP12. By default, both jumpers are inserted on jumper block header J11.

Programming Header J12

As shown in

Figure 12-15, page 99

, Header J12 accepts a JTAG parallel programming cable

to program the on-board SPI Flash.

Multi-Package Layout

STMicroelectronics was rather clever when they defined the package layout for the

M25Pxx SPI serial Flash family. The Spartan-3E Starter Kit board supports all three of the

package types used for the 16 Mbit device, as shown in

Figure 12-19

. By default, the board

ships with the 8-lead, 8x6 mm MLP package. The multi-package layout also supports the 8-

pin SOIC package and the 16-pin SOIC package. Pin 1 for the 8-pin SOIC and MLP

packages is located in the top-left corner. However, pin 1 for the 16-pin SOIC package is

located in the top-right corner, because the package is rotated 90

°

. The 16-pin SOIC

package also have four pins on each side that do not connect on the board. These pins must

be left floating. Why support multiple packages? In a word, flexibility. The multi-package

layout provides ...

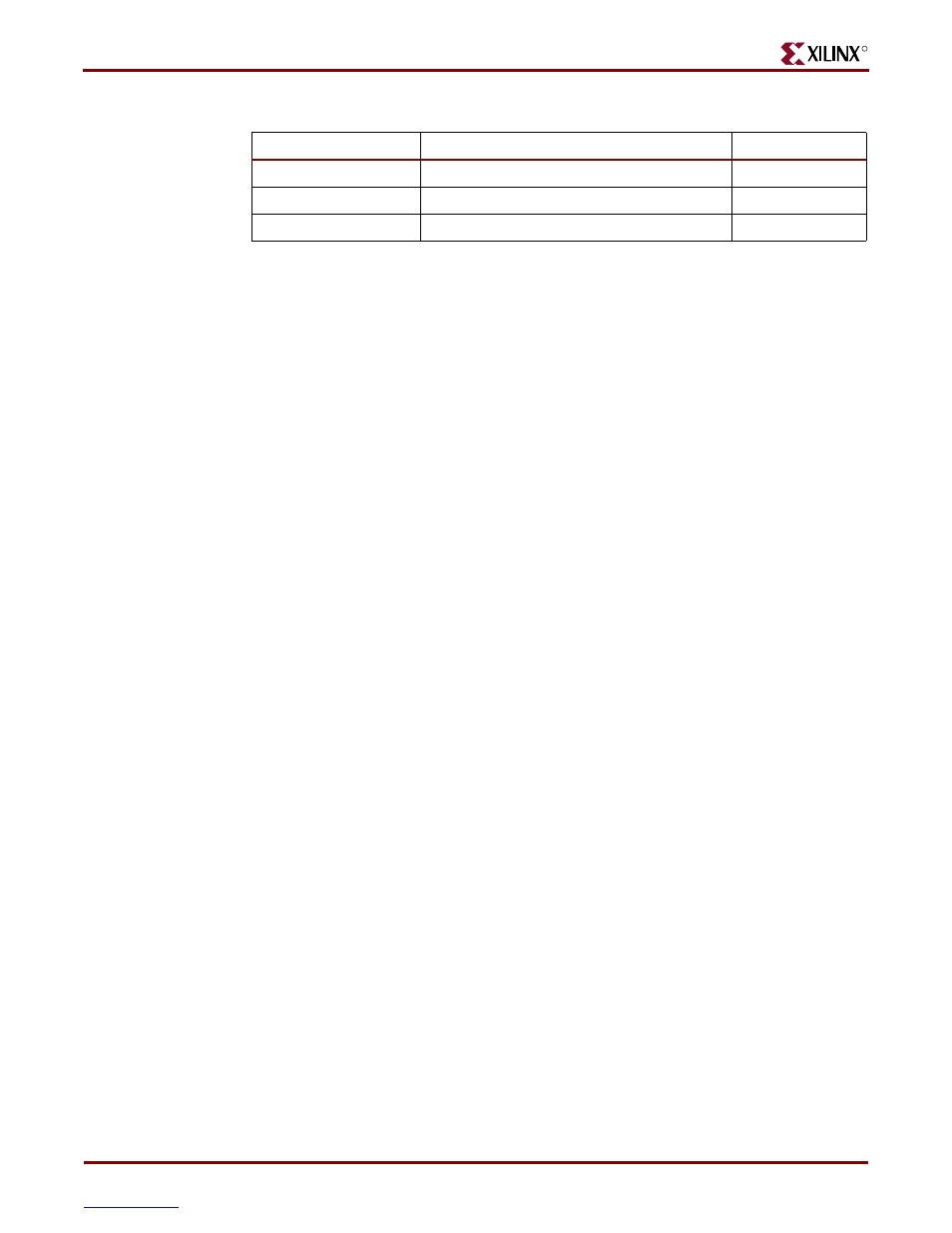

AD_CONV

Analog-to-Digital Converter (ADC)

0

SF_CE0

StrataFlash Parallel Flash PROM

1

FPGA_INIT_B

Platform Flash PROM

1

Table 12-3:

Disable Other Devices on SPI Bus

Signal

Disabled Device

Disable Value