3 timing, 1 clocks, video data, sync timing, C host port timing – Texas Instruments TVP5147M1PFP User Manual

Page 89

Electrical Specifications

81

SLES140A—March 2007

TVP5147M1PFP

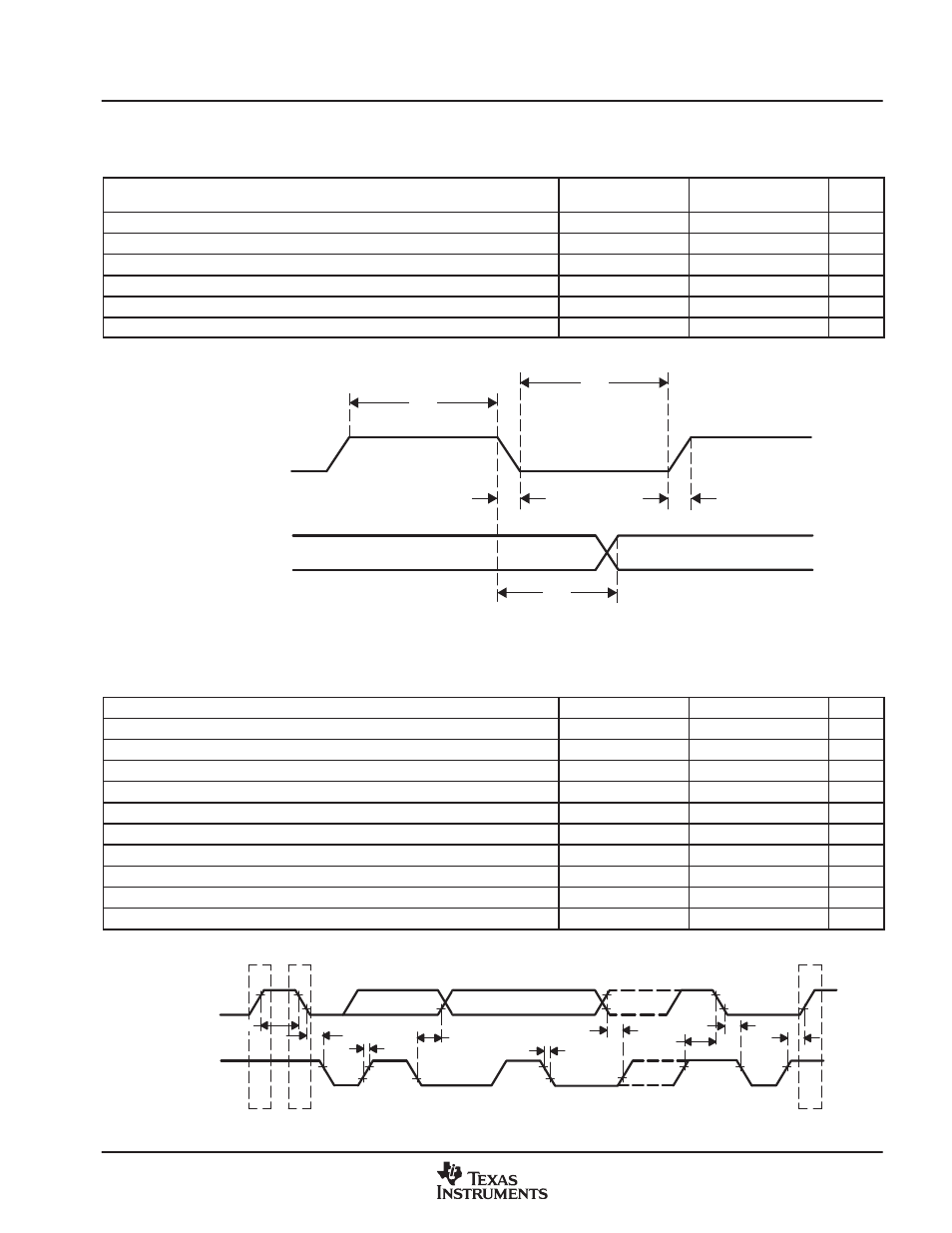

3.3.3 Timing

3.3.3.1

Clocks, Video Data, Sync Timing

PARAMETER

TEST CONDITIONS

(see NOTE 1)

MIN

TYP

MAX

UNIT

Duty cycle DATACLK

45%

50%

55%

t1

High time, DATACLK

18.5

ns

t2

Low time, DATACLK

18.5

ns

t3

Fall time, DATACLK

90% to 10%

4

ns

t4

Rise time, DATACLK

10% to 90%

4

ns

t5

Output delay time

10

ns

NOTE 1: CL = 15 pF

t1

DATACLK

Y, C, AVID, VS, HS, FID

t4

t2

t3

t5

VOH

VOL

Valid Data

Valid Data

VOH

VOL

Figure 3−1. Clocks, Video Data, and Sync Timing

3.3.3.2

I

2

C Host Port Timing

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

t1

Bus free time between STOP and START

1.3

µ

s

t2

Data hold time

0

0.9

µ

s

t3

Data setup time

100

ns

t4

Setup time for a (repeated) START condition

0.6

µ

s

t5

Setup time for a STOP condition

0.6

ns

t6

Hold time for a (repeated) START condition

0.6

µ

s

t7

Rise time VC1(SDA) and VC0(SCL) signal

250

ns

t8

Fall time VC1(SDA) and VC0(SCL) signal

250

ns

Cb

Capacitive load for each bus line

400

pF

fI2C

I2C clock frequency

400

kHz

t5

Stop Start

VC1 (SDA)

t1

t6

t7

t2

t8

t3

t4

t6

VC0 (SCL)

Data

Stop

Change

Data

Figure 3−2. I

2

C Host Port Timing