63 status request register, 64 vertical line count register, 65 agc decrement delay register – Texas Instruments TVP5147M1PFP User Manual

Page 68

Functional Description

60

SLES140A—March 2007

TVP5147M1PFP

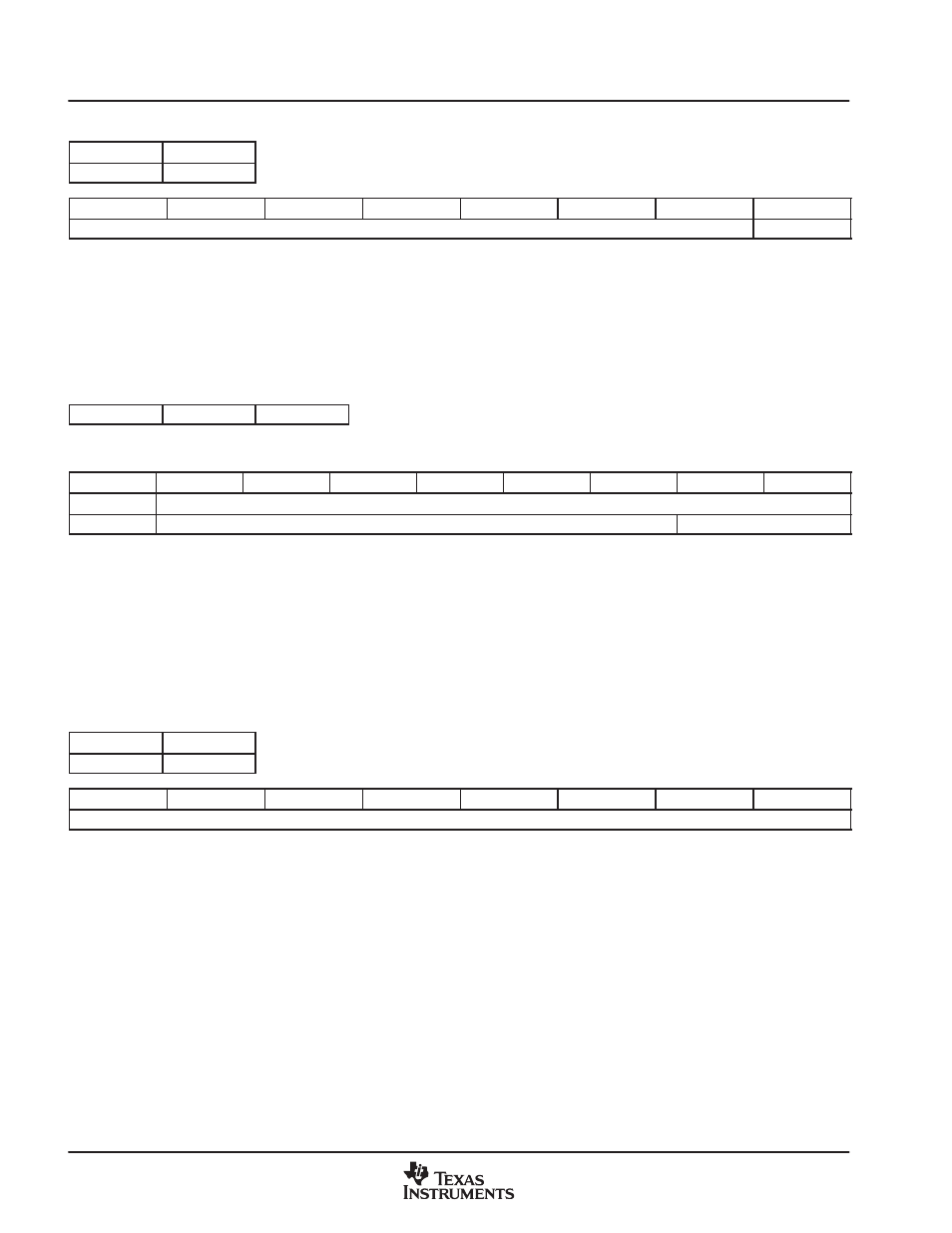

2.11.63 Status Request Register

Subaddress

97h

Default

00h

7

6

5

4

3

2

1

0

Reserved

Capture

Capture:

Setting a 1b in this register causes the internal processor to capture the current settings of the AGC status

and the vertical line count registers. Since this capture is not immediate, it is necessary to check for completion

of the capture by reading the capture bit repeatedly after setting it and waiting for it to be cleared by the internal

processor. Once the capture bit is 0b, the AGC status and vertical line counters (3Ch/3Dh and 9Ah/9Bh) have

been updated and can be safely read in any order.

2.11.64 Vertical Line Count Register

Subaddress

9Ah

9Bh

Read only

Subaddress

7

6

5

4

3

2

1

0

9Ah

Vertical line [7:0]

9Bh

Reserved

Vertical line [9:8]

Vertical line [9:0] represents the detected a total number of lines from the previous frame. This can be used

with nonstandard video signals such as a VCR in trick mode to synchronize downstream video circuitry.

Since this register is a double-byte register, it is necessary to capture the setting into the register to ensure

that the value is not updated between reading the lower and upper bytes. In order to cause this register to

capture the current settings, bit 0 of the status request register (subaddress 97h) must be set to a 1b. Once

the internal processor has updated and can be read. Either byte may be read first since no further update will

occur until bit 0 of 97h is set to 1b again.

2.11.65 AGC Decrement Delay Register

Subaddress

9Eh

Default

00h

7

6

5

4

3

2

1

0

AGC decrement delay [7:0]

AGC decrement delay [7:0]: Number of frames to delay gain decrements

1111 1111 = 255

0001 1110 = 30 (default)

0000 0000 = 0