84 interrupt raw status 1 register, 85 interrupt status 0 register – Texas Instruments TVP5147M1PFP User Manual

Page 76

Functional Description

68

SLES140A—March 2007

TVP5147M1PFP

CC F1: CC field 1 data available unmasked

0 = Not available

1 = Available

Line: Line number interrupt unmasked

0 = Not available

1 = Available

The host interrupt raw status 0 and 1 registers represent the interrupt status without applying mask bits.

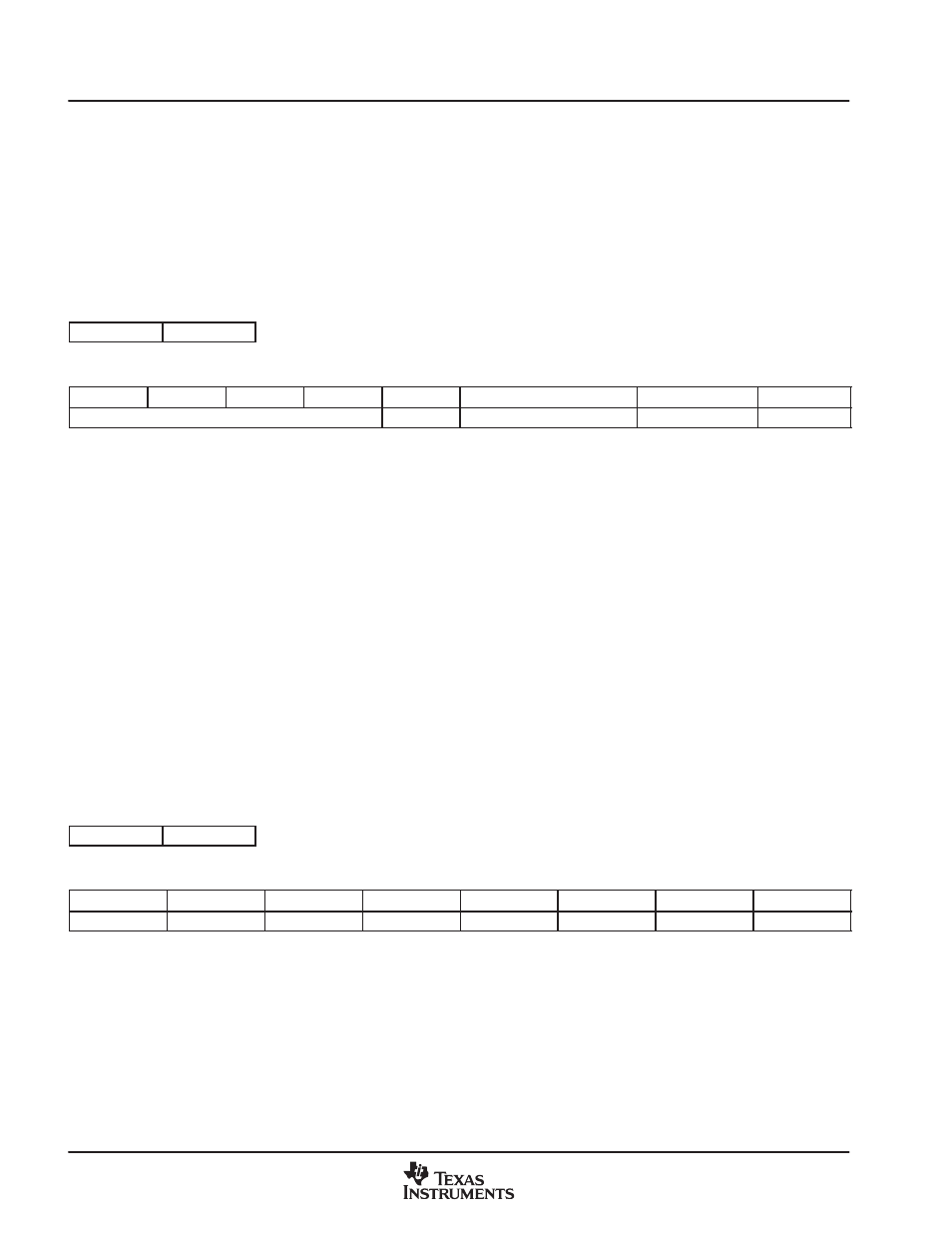

2.11.84 Interrupt Raw Status 1 Register

Subaddress

F1h

Read only

7

6

5

4

3

2

1

0

Reserved

H/V lock

Macrovision status changed

Standard changed

FIFO full

H/V lock: unmasked

0 = H/V lock status unchanged

1 = H/V lock status changed

Macrovision status changed: unmasked

0 = Macrovision status unchanged

1 = Macrovision status changed

Standard changed: unmasked

0 = Video standard unchanged

1 = Video standard changed

FIFO full: unmasked

0 = FIFO not full

1 = FIFO was full during write to FIFO

The FIFO full error flag is set when the current line of VBI data cannot enter the FIFO. For example, if the FIFO

has only 10 bytes left and teletext is the current VBI line, then the FIFO full error flag is set, but no data is written

because the entire teletext line does not fit. However, if the next VBI line is closed caption requiring only 2 bytes

of data plus the header, then this goes into the FIFO even if the full error flag is set.

2.11.85 Interrupt Status 0 Register

Subaddress

F2h

Read only

7

6

5

4

3

2

1

0

FIFO THRS

TTX

WSS

VPS

VITC

CC F2

CC F1

Line

FIFO THRS: FIFO threshold passed, masked

0 = Not passed

1 = Passed

TTX: Teletext data available masked

0 = Not available

1 = Available

WSS: WSS data available masked

0 = Not available

1 = Available