90 interrupt clear 1 register – Texas Instruments TVP5147M1PFP User Manual

Page 80

Functional Description

72

SLES140A—March 2007

TVP5147M1PFP

Line: Line number interrupt clear

0 = Disabled (default)

1 = Clear bit 0 (line interrupt available) in the interrupt status 0 register at subaddress F2h

The host interrupt clear 0 and 1 registers are used by the external processor to clear the interrupt status bits

in the host interrupt status 0 and 1 registers. When no nonmasked interrupts remain set in the registers, the

external interrupt terminal also becomes inactive.

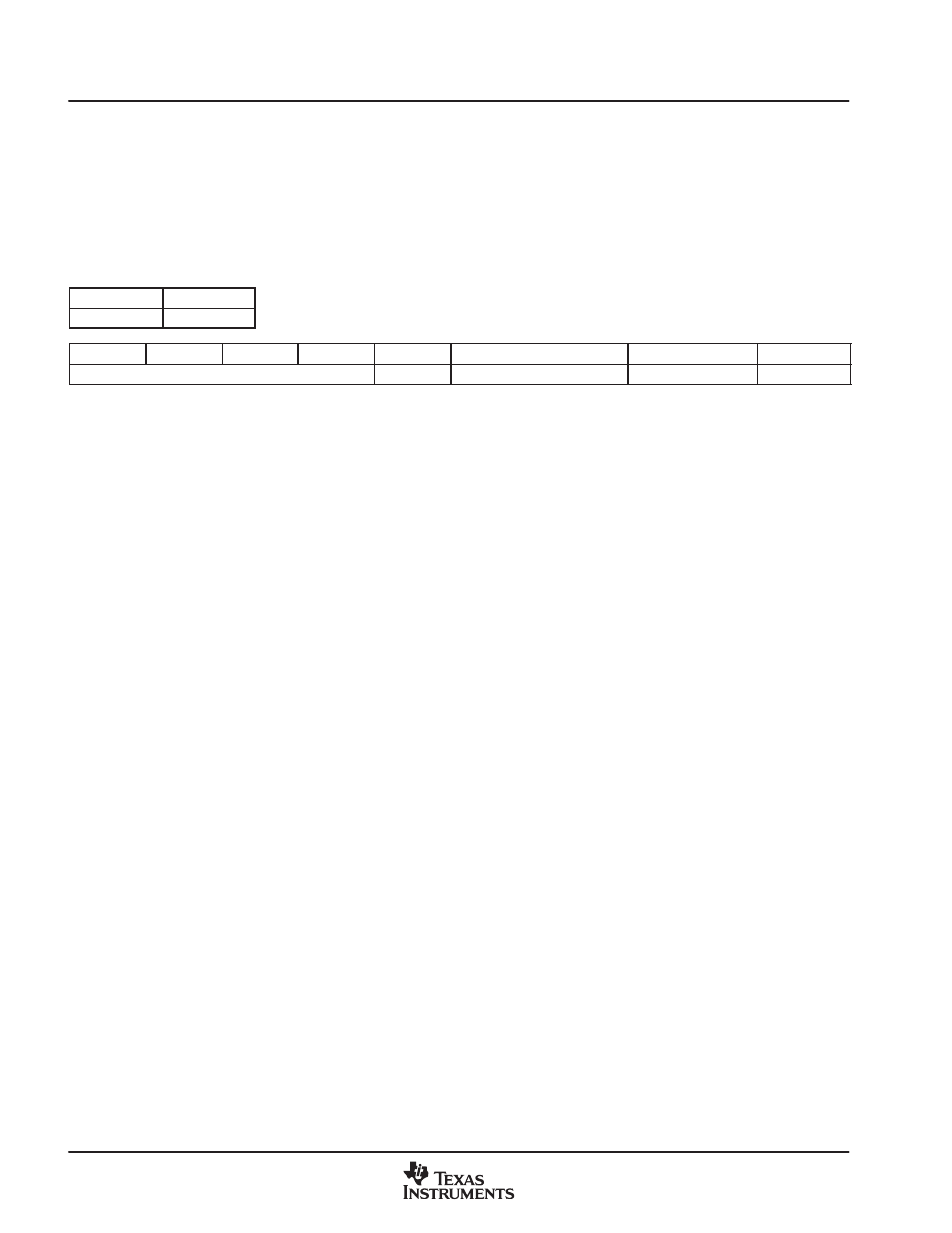

2.11.90 Interrupt Clear 1 Register

Subaddress

F7h

Default

00h

7

6

5

4

3

2

1

0

Reserved

H/V lock

Macrovision status changed

Standard changed

FIFO full

H/V lock: Clear H/V lock status changed flag

0 = H/V lock status unchanged

1 = H/V lock status changed

Macrovision status changed: Clear Macrovision status changed flag

0 = No effect (default)

1 = Clear bit 2 (Macrovision status changed) in the interrupt status 1 register at subaddress F3h and the

interrupt raw status 1 register at subaddress F1h

Standard changed: Clear standard changed flag

0 = No effect (default)

1 = Clear bit 1 (video standard changed) in the interrupt status 1 register at subaddress F3h and the

interrupt raw status 1 register at subaddress F1h

FIFO full: Clear FIFO full flag

0 = No effect (default)

1 = Clear bit 0 (FIFO full flag) in the interrupt status 1 register at subaddress F3h and the interrupt raw

status 1 register at subaddress F1h