15 chrominance processing control 2 register, 16 avid start pixel register – Texas Instruments TVP5147M1PFP User Manual

Page 45

Functional Description

37

SLES140A—March 2007

TVP5147M1PFP

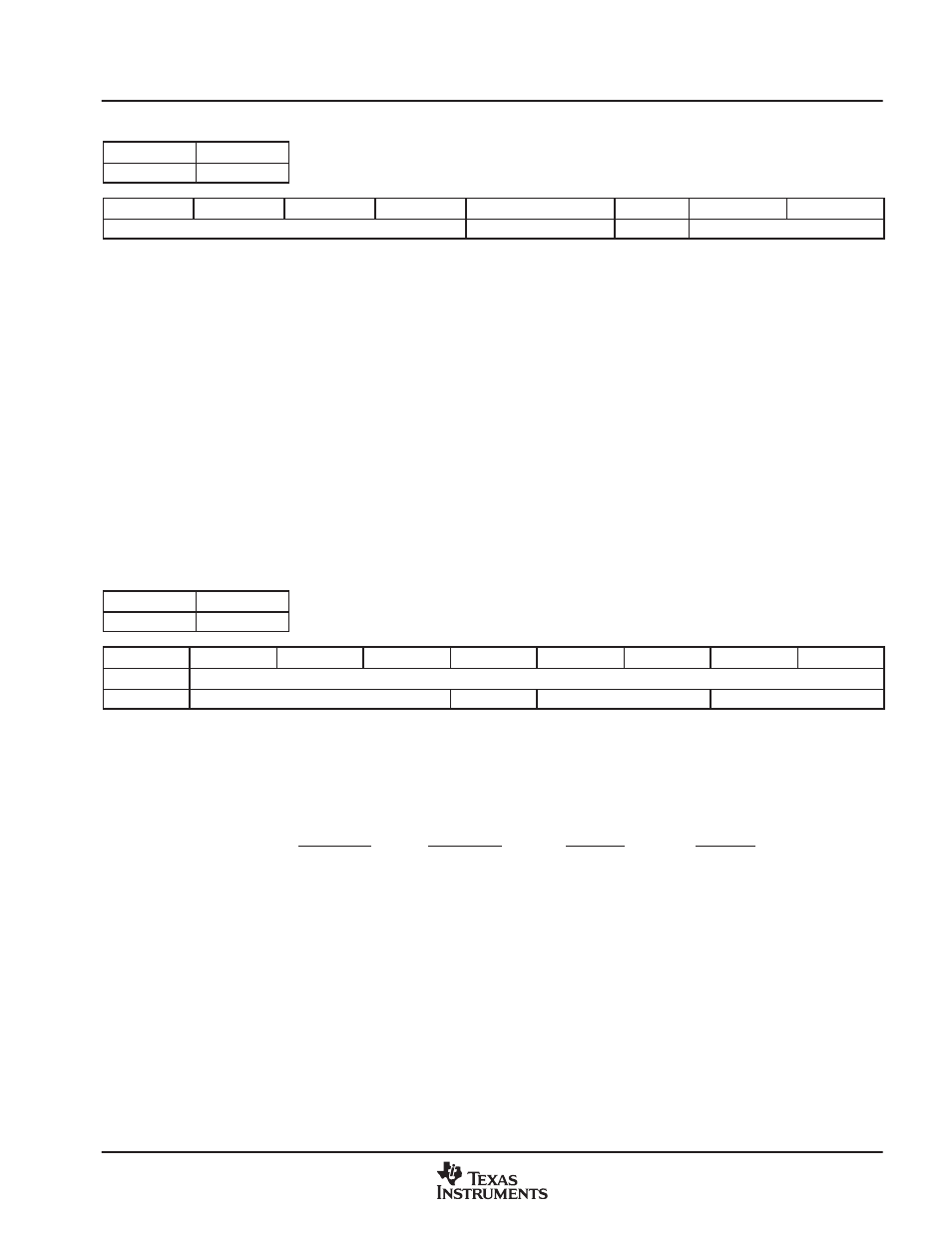

2.11.15 Chrominance Processing Control 2 Register

Subaddress

0Eh

Default

0Eh

7

6

5

4

3

2

1

0

Reserved

PAL compensation

WCF

Chrominance filter select [1:0]

PAL compensation:

0 = Disabled

1 = Enabled (default)

Wideband chroma LPF filter (WCF):

0 = Disabled

1 = Enabled (default)

Chrominance filter select [1:0]:

00 = Disabled

01 = Notch 1

10 = Notch 2 (default)

11 = Notch 3

See Figure 2−6 and Figure 2−7 for characteristics.

2.11.16 AVID Start Pixel Register

Subaddress

16h−17h

Default

055h

Subaddress

7

6

5

4

3

2

1

0

16h

AVID start [7:0]

17h

Reserved

AVID active

Reserved

AVID start [9:8]

AVID active:

0 = AVID out active in VBLK (default)

1 = AVID out inactive in VBLK

AVID start [9:0]: AVID start pixel number, this is an absolute pixel location from HSYNC start pixel 0.

NTSC 601

NTSC Sqp

PAL 601

PAL Sqp

default

85 (55h)

86 (56h)

88 (58h)

103 (67h)

The TVP5147M1 decoder updates the AVID start only when the AVID start MSB byte is written to. If the user

changes these registers, then the TVP5147M1 decoder retains values in different modes until this device

resets. The AVID start pixel register also controls the position of the SAV code.