27 output formatter 1 register, 28 output formatter 2 register – Texas Instruments TVP5147M1PFP User Manual

Page 49

Functional Description

41

SLES140A—March 2007

TVP5147M1PFP

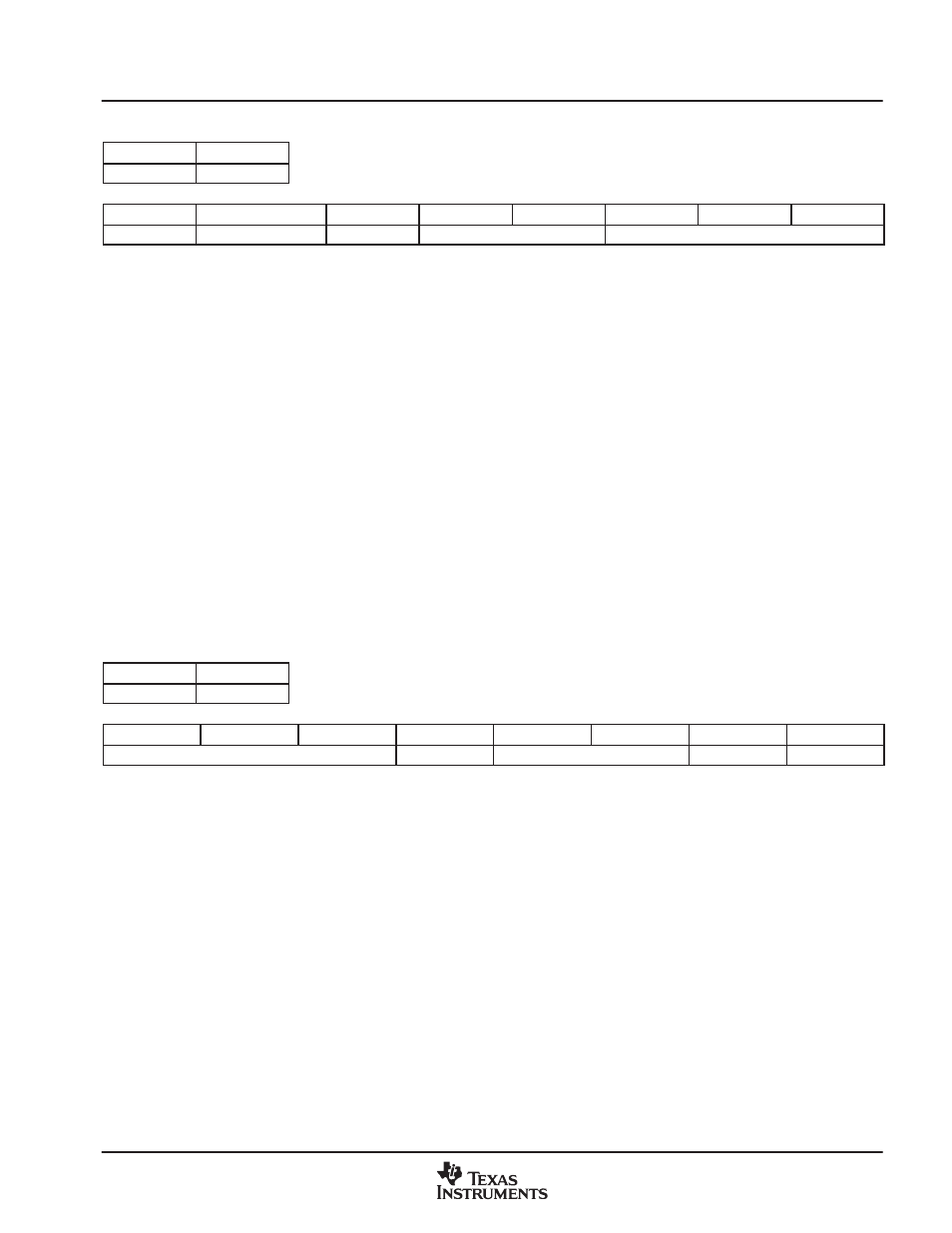

2.11.27 Output Formatter 1 Register

Subaddress

33h

Default

40h

7

6

5

4

3

2

1

0

Reserved

YCbCr code range

CbCr code

Reserved

Output format [2:0]

YCbCr output code range:

0 = ITU-R BT.601 coding range (Y ranges from 64 to 940. Cb and Cr range from 64 to 960.)

1 = Extended coding range (Y, Cb, and Cr range from 4 to 1016.) (default)

CbCr code format:

0 = Offset binary code (2s complement + 512) (default)

1 = Straight binary code (2s complement)

Output format [2:0]:

000 = 10-bit 4:2:2 (pixel x 2 rate) with embedded syncs (ITU-R BT.656) (default)

001 = 20-bit 4:2:2 (pixel rate) with separate syncs

010 = Reserved

011 = 10-bit 4:2:2 with separate syncs

100−111= Reserved

NOTE: 10-bit mode is also used for the raw VBI output mode when bit 4 (VBI raw) in the

luminance processing control 1 register at subaddress 06h is set (see Section 2.11.7).

2.11.28 Output Formatter 2 Register

Subaddress

34h

Default

00h

7

6

5

4

3

2

1

0

Reserved

Data enable

Black Screen [1:0]

CLK polarity

Clock enable

Data enable: Y[9:0] AND C[9:0] output enable

0 = Y[9:0] and C[9:0] high impedance (default)

1 = Y [9:0] and C[9:0] active

Black Screen [1:0]:

00 = Normal operation (default)

01 = Black screen out when TVP5147M1 detects lost lock (using with tuner input but not with VCR)

10 = Black screen out

11 = Black screen out

CLK polarity:

0 = Data clocked out on the falling edge of DATACLK (default)

1 = Data clocked out on the rising edge of DATACLK

Clock enable:

0 = DATACLK outputs are high-impedance (default).

1 = DATACLK outputs are enabled.