86 interrupt status 1 register – Texas Instruments TVP5147M1PFP User Manual

Page 77

Functional Description

69

SLES140A—March 2007

TVP5147M1PFP

VPS: VPS data available masked

0 = Not available

1 = Available

VITC: VITC data available masked

0 = Not available

1 = Available

CC F2: CC field 2 data available masked

0 = Not available

1 = Available

CC F1: CC field 1 data available masked

0 = Not available

1 = Available

Line: Line number interrupt masked

0 = Not available

1 = Available

The interrupt status 0 and 1 registers represent the interrupt status after applying mask bits. Therefore, the

status bits are the result of a logical AND between the raw status and mask bits. The external interrupt terminal

is derived from this register as an OR function of all nonmasked interrupts in this register.

Reading data from the corresponding register does not clear the status flags automatically. These flags are

reset using the corresponding bits in interrupt clear 0 and 1 registers.

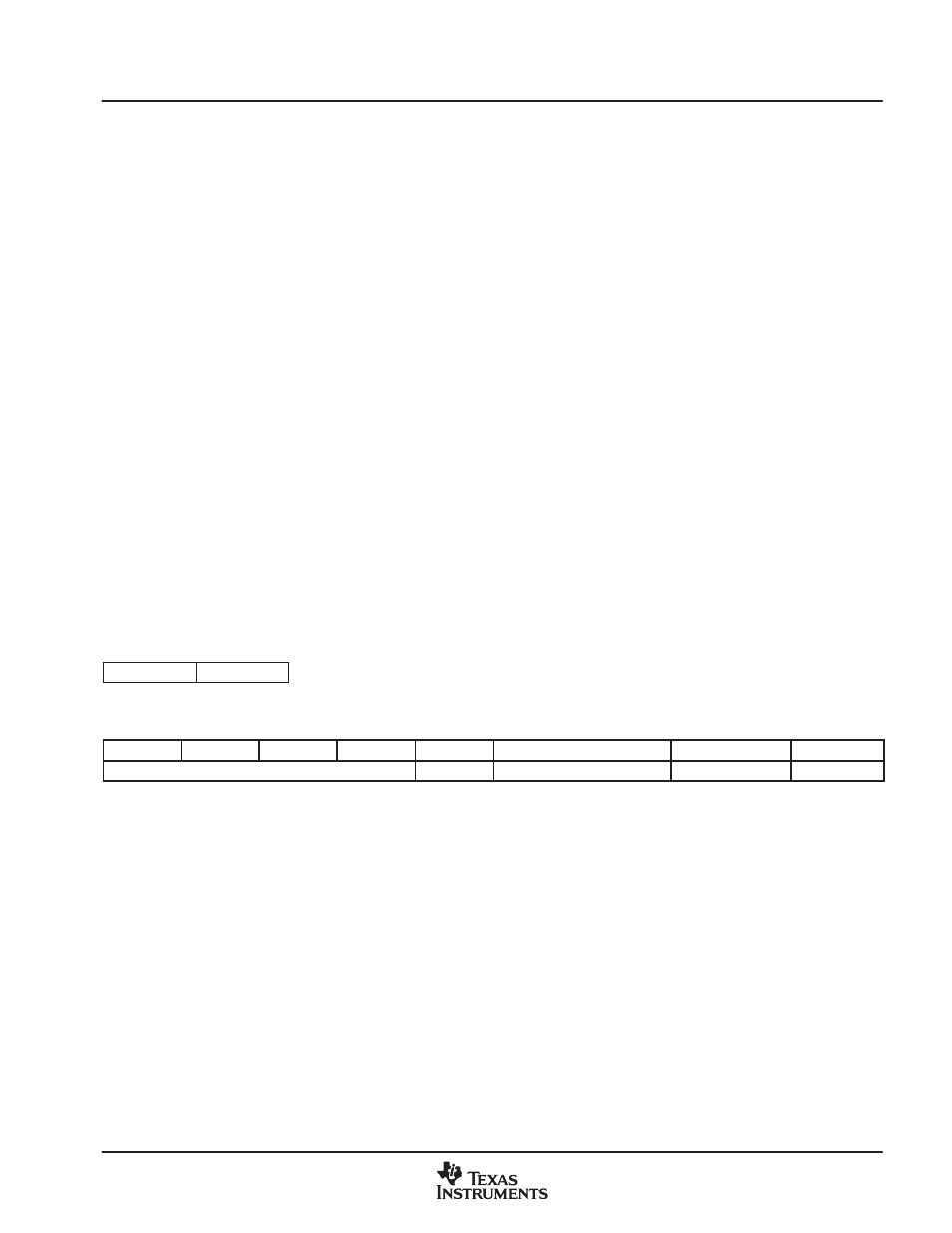

2.11.86 Interrupt Status 1 Register

Subaddress

F3h

Read only

7

6

5

4

3

2

1

0

Reserved

H/V lock

Macrovision status changed

Standard changed

FIFO full

H/V lock: H/V lock status changed mask

0 = H/V lock status unchanged

1 = H/V lock status changed

Macrovision status changed: Macrovision status changed masked

0 = Macrovision status not changed

1 = Macrovision status changed

Standard changed: Standard changed masked

0 = Video standard not changed

1 = Video standard changed

FIFO full: full status of FIFO masked

0 = FIFO not full

1 = FIFO was full during write to FIFO, see the interrupt mask 1 register at subaddress F5h for details (see

Section 2.11.88)