87 interrupt mask 0 register – Texas Instruments TVP5147M1PFP User Manual

Page 78

Functional Description

70

SLES140A—March 2007

TVP5147M1PFP

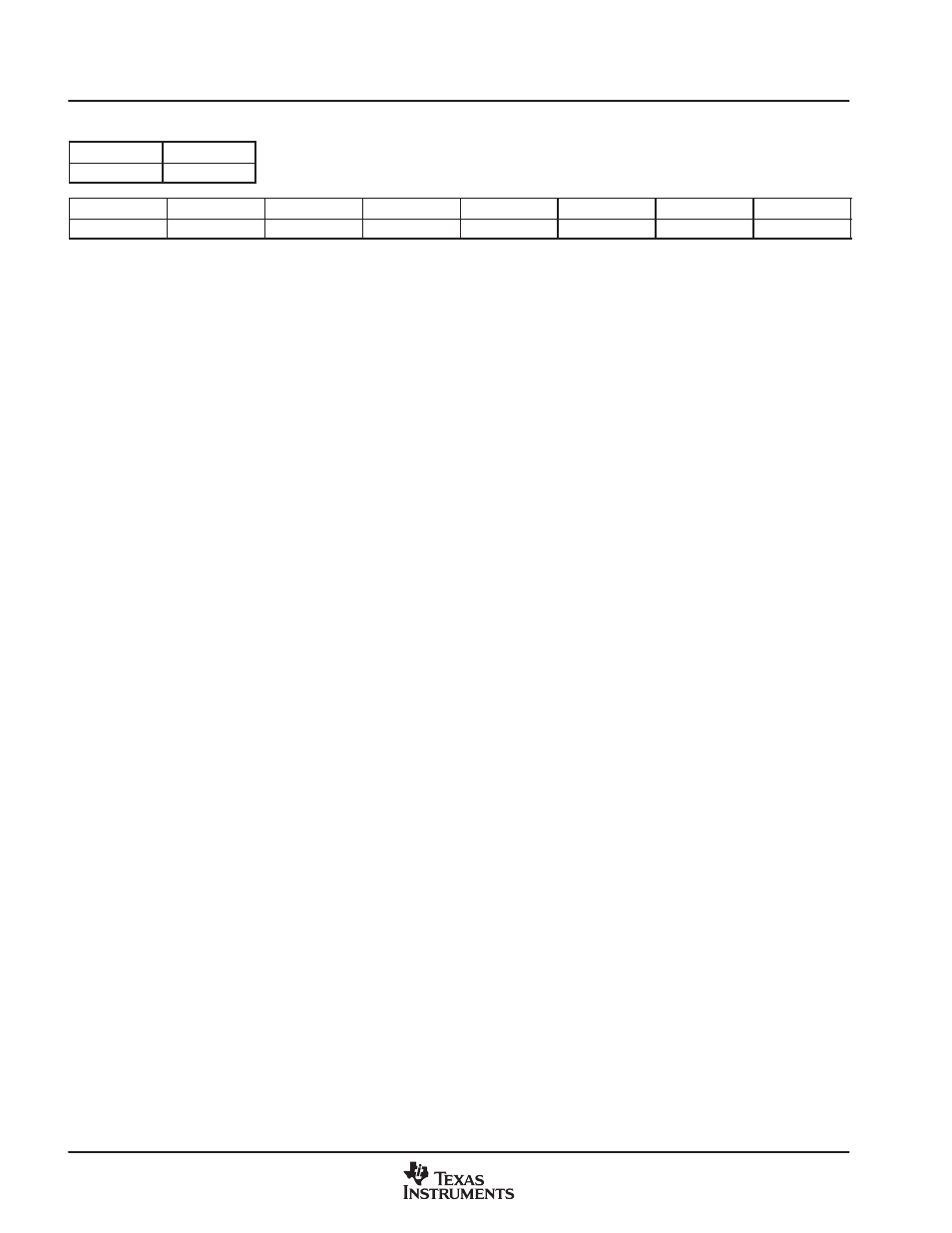

2.11.87 Interrupt Mask 0 Register

Subaddress

F4h

Default

00h

7

6

5

4

3

2

1

0

FIFO THRS

TTX

WSS

VPS

VITC

CC F2

CC F1

Line

FIFO THRS: FIFO threshold passed mask

0 = Disabled (default)

1 = Enabled FIFO_THRES interrupt

TTX: Teletext data available mask

0 = Disabled (default)

1 = Enabled TTX available interrupt

WSS: WSS data available mask

0 = Disabled (default)

1 = Enabled WSS available interrupt

VPS: VPS data available mask

0 = Disabled (default)

1 = Enabled VPS available interrupt

VITC: VITC data available mask

0 = Disabled (default)

1 = Enabled VITC available interrupt

CC F2: CC field 2 data available mask

0 = Disabled (default)

1 = Enabled CC_field 2 available interrupt

CC F1: CC field 1 data available mask

0 = Disabled (default)

1 = Enabled CC_field 1 available interrupt

Line: Line number interrupt mask

0 = Disabled (default)

1 = Enabled Line_INT interrupt

The host interrupt mask 0 and 1 registers can be used by the external processor to mask unnecessary interrupt

sources for the interrupt status 0 and 1 register bits, and for the external interrupt terminal. The external

interrupt is generated from all nonmasked interrupt flags.