Texas Instruments TMS320F2802 User Manual

Page 84

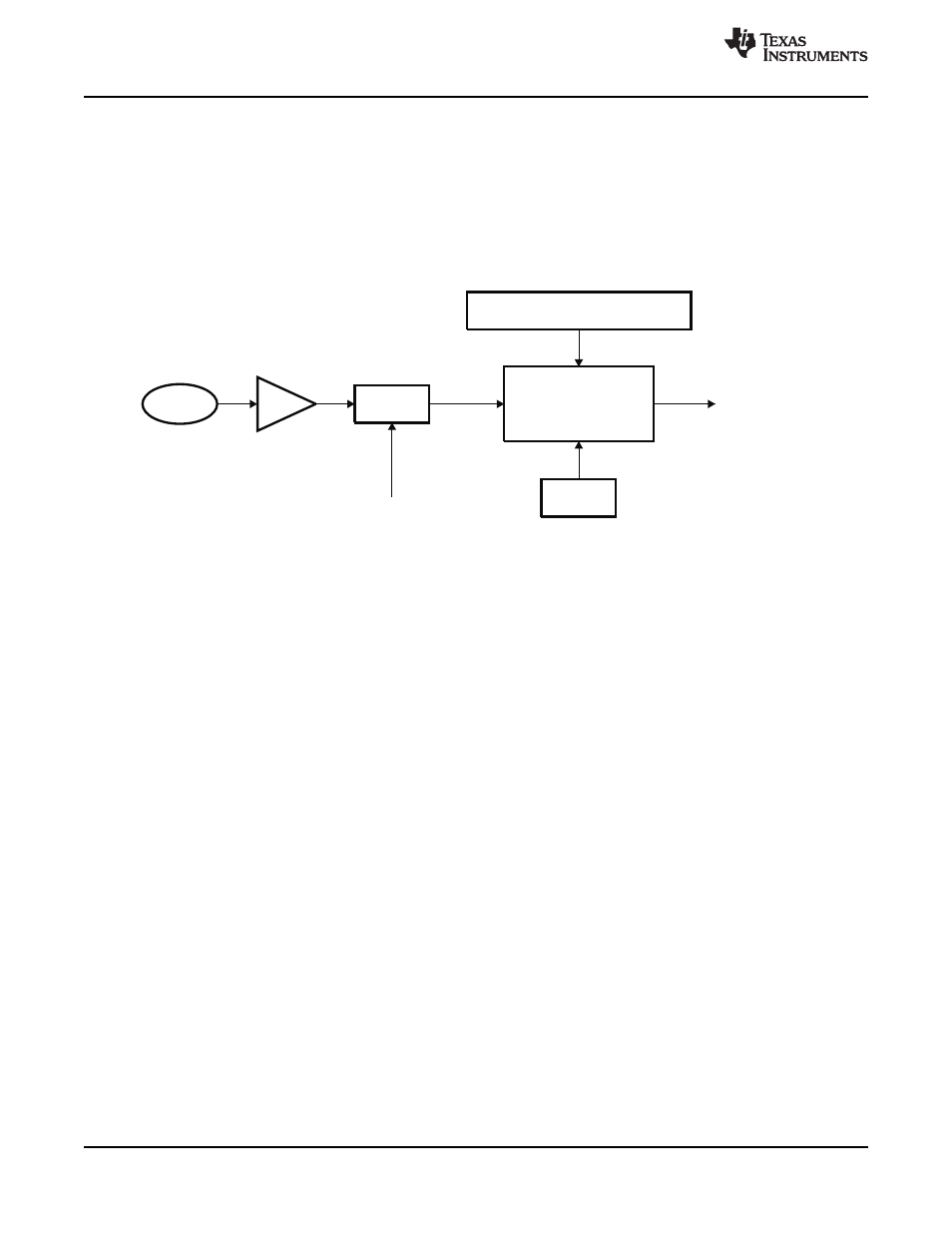

GPyCTRL Reg

SYNC

SYSCLKOUT

Qualification

Input Signal

Qualified by

3 or 6 Samples

GPIOx

Time Between Samples

GPxQSEL

Number of Samples

, , ,

SPRS230N – OCTOBER 2003 – REVISED MAY 2012

The user can select the type of input qualification for each GPIO pin via the GPxQSEL1/2 registers from

four choices:

•

Synchronization To SYSCLKOUT Only (GPxQSEL1/2 = 0,0): This is the default mode of all GPIO pins

at reset and it simply synchronizes the input signal to the system clock (SYSCLKOUT).

•

Qualification Using Sampling Window (GPxQSEL1/2 = 0,1 and 1,0): In this mode the input signal, after

synchronization to the system clock (SYSCLKOUT), is qualified by a specified number of cycles before

the input is allowed to change.

Figure 4-17. Qualification Using Sampling Window

•

The sampling period is specified by the QUALPRD bits in the GPxCTRL register and is configurable in

groups of 8 signals. It specifies a multiple of SYSCLKOUT cycles for sampling the input signal. The

sampling window is either 3-samples or 6-samples wide and the output is only changed when ALL

samples are the same (all 0s or all 1s) as shown in

(for 6-sample mode).

•

No Synchronization (GPxQSEL1/2 = 1,1): This mode is used for peripherals where synchronization is

not required (synchronization is performed within the peripheral).

Due to the multi-level multiplexing that is required on the 280x device, there may be cases where a

peripheral input signal can be mapped to more then one GPIO pin. Also, when an input signal is not

selected, the input signal will default to either a 0 or 1 state, depending on the peripheral.

84

Peripherals

Copyright © 2003–2012, Texas Instruments Incorporated

Product Folder Link(s):