Texas Instruments TMS320F2802 User Manual

Page 19

,

,

,

SPRS230N – OCTOBER 2003 – REVISED MAY 2012

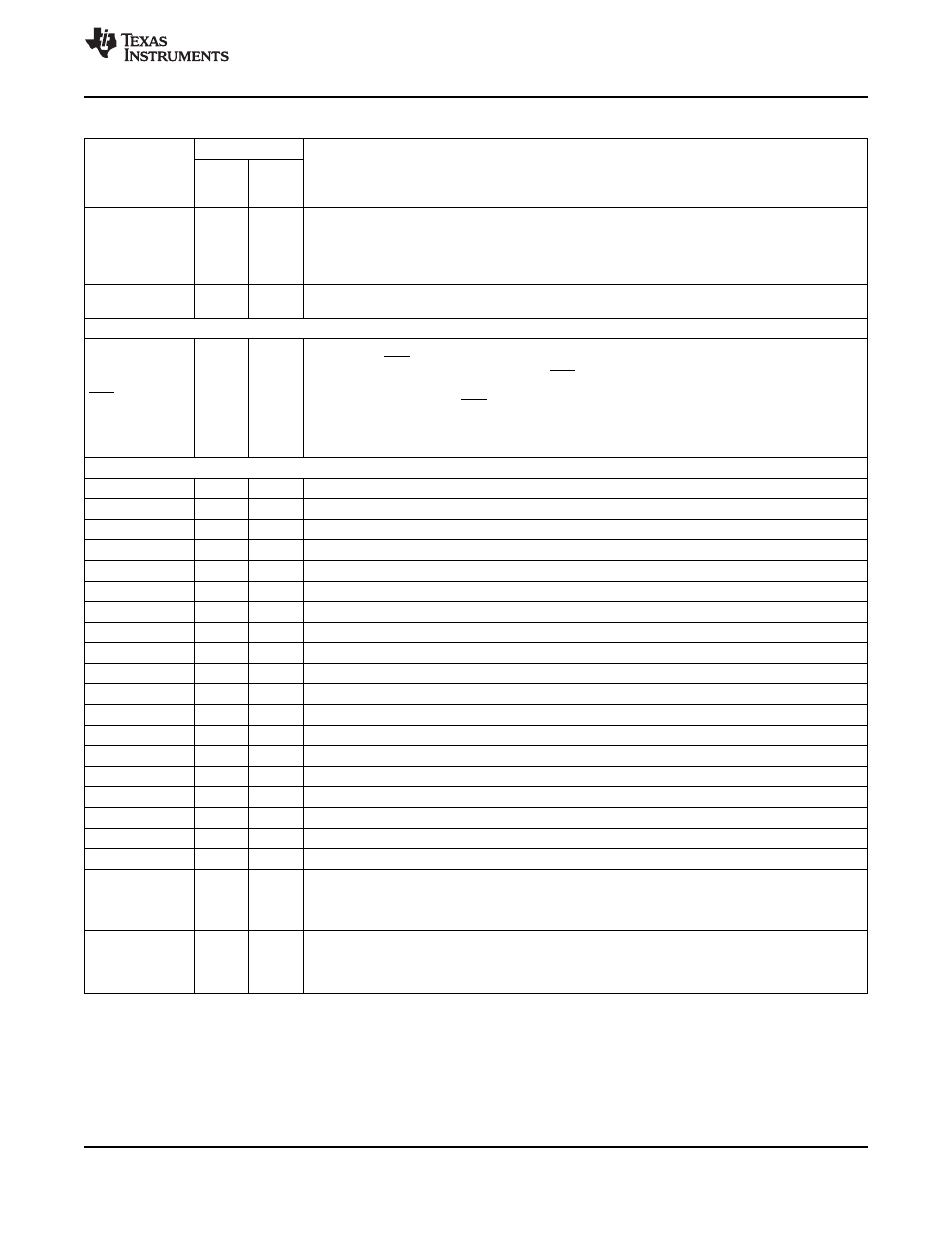

Table 2-3. Signal Descriptions (continued)

PIN NO.

GGM/

NAME

DESCRIPTION

(1)

PZ

ZGM

PIN #

BALL #

Internal/External Oscillator Input. To use the internal oscillator, a quartz crystal or a ceramic

resonator may be connected across X1 and X2. The X1 pin is referenced to the 1.8-V core digital

X1

88

E6

power supply. A 1.8-V external oscillator may be connected to the X1 pin. In this case, the XCLKIN

pin must be connected to ground. If a 3.3-V external oscillator is used with the XCLKIN pin, X1 must

be tied to GND. (I)

Internal Oscillator Output. A quartz crystal or a ceramic resonator may be connected across X1 and

X2

86

C6

X2. If X2 is not used it must be left unconnected. (O)

RESET

Device Reset (in) and Watchdog Reset (out).

Device reset. XRS causes the device to terminate execution. The PC will point to the address

contained at the location 0x3FFFC0. When XRS is brought to a high level, execution begins at the

location pointed to by the PC. This pin is driven low by the DSP when a watchdog reset occurs.

XRS

78

B8

During watchdog reset, the XRS pin is driven low for the watchdog reset duration of 512 OSCCLK

cycles. (I/OD,

↑

)

The output buffer of this pin is an open-drain with an internal pullup. It is recommended that this pin

be driven by an open-drain device.

ADC SIGNALS

ADCINA7

16

F3

ADC Group A, Channel 7 input (I)

ADCINA6

17

F4

ADC Group A, Channel 6 input (I)

ADCINA5

18

G4

ADC Group A, Channel 5 input (I)

ADCINA4

19

G1

ADC Group A, Channel 4 input (I)

ADCINA3

20

G2

ADC Group A, Channel 3 input (I)

ADCINA2

21

G3

ADC Group A, Channel 2 input (I)

ADCINA1

22

H1

ADC Group A, Channel 1 input (I)

ADCINA0

23

H2

ADC Group A, Channel 0 input (I)

ADCINB7

34

K5

ADC Group B, Channel 7 input (I)

ADCINB6

33

H4

ADC Group B, Channel 6 input (I)

ADCINB5

32

K4

ADC Group B, Channel 5 input (I)

ADCINB4

31

J4

ADC Group B, Channel 4 input (I)

ADCINB3

30

K3

ADC Group B, Channel 3 input (I)

ADCINB2

29

H3

ADC Group B, Channel 2 input (I)

ADCINB1

28

J3

ADC Group B, Channel 1 input (I)

ADCINB0

27

K2

ADC Group B, Channel 0 input (I)

ADCLO

24

J1

Low Reference (connect to analog ground) (I)

ADCRESEXT

38

F5

ADC External Current Bias Resistor. Connect a 22-k

Ω

resistor to analog ground.

ADCREFIN

35

J5

External reference input (I)

Internal Reference Positive Output. Requires a low ESR (under 1.5

Ω

) ceramic bypass capacitor of

2.2

μ

F to analog ground. (O)

ADCREFP

37

G5

NOTE: Use the ADC Clock rate to derive the ESR specification from the capacitor data sheet that is

used in the system.

Internal Reference Medium Output. Requires a low ESR (under 1.5

Ω

) ceramic bypass capacitor of

2.2

μ

F to analog ground. (O)

ADCREFM

36

H5

NOTE: Use the ADC Clock rate to derive the ESR specification from the capacitor data sheet that is

used in the system.

Copyright © 2003–2012, Texas Instruments Incorporated

Introduction

19

Product Folder Link(s):