7 clock requirements and characteristics – Texas Instruments TMS320F2802 User Manual

Page 105

,

,

,

SPRS230N – OCTOBER 2003 – REVISED MAY 2012

6.7

Clock Requirements and Characteristics

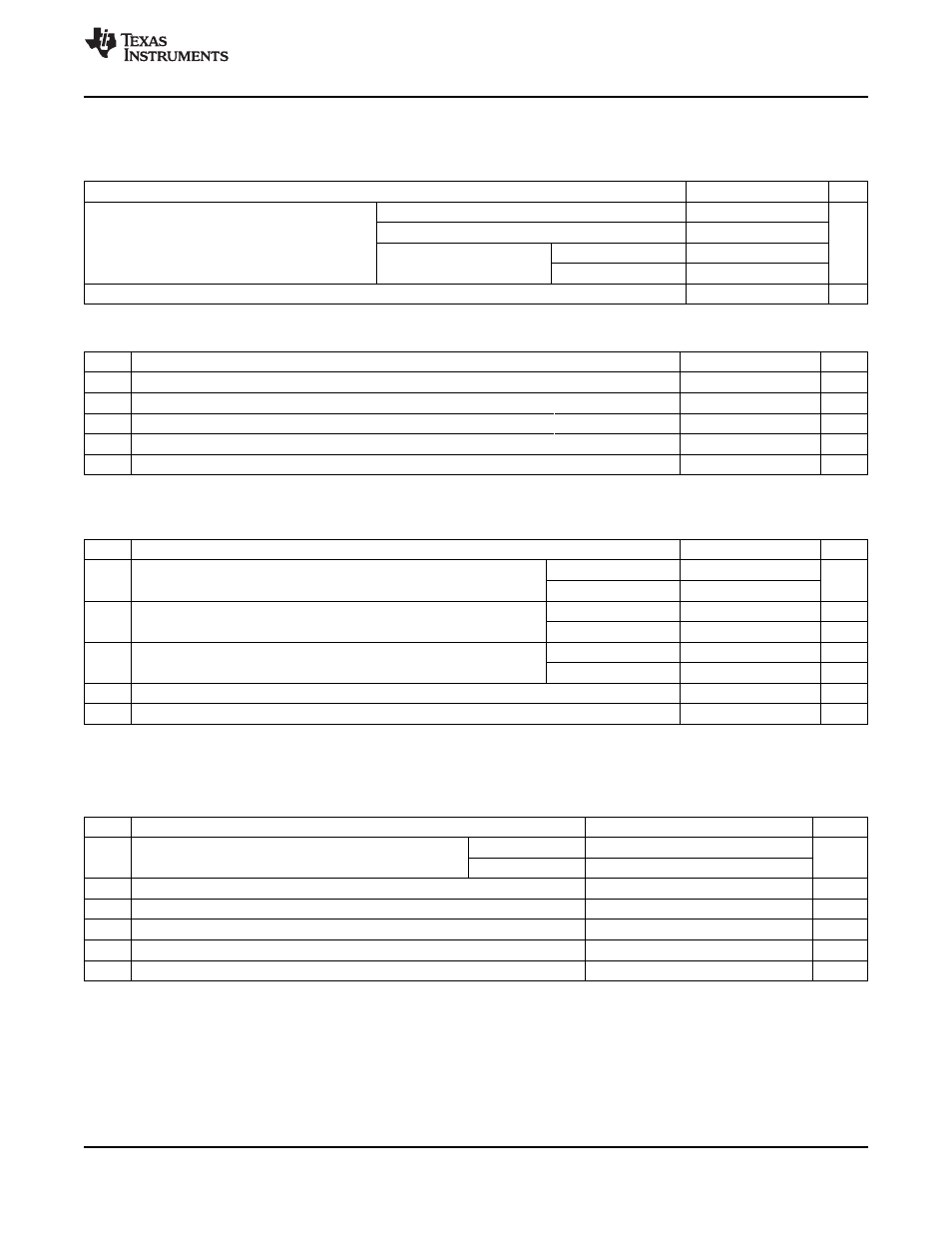

Table 6-8. Input Clock Frequency

PARAMETER

MIN

TYP

MAX

UNIT

Resonator (X1/X2)

20

35

Crystal (X1/X2)

20

35

f

x

Input clock frequency

MHz

100-MHz device

4

100

External oscillator/clock

source (XCLKIN or X1 pin)

60-MHz device

4

60

f

l

Limp mode SYSCLKOUT frequency range (with /2 enabled)

1–5

MHz

Table 6-9. XCLKIN

(1)

Timing Requirements - PLL Enabled

NO.

MIN

MAX

UNIT

C8

t

c(CI)

Cycle time, XCLKIN

33.3

200

ns

C9

t

f(CI)

Fall time, XCLKIN

6

ns

C10

t

r(CI)

Rise time, XCLKIN

6

ns

C11

t

w(CIL)

Pulse duration, XCLKIN low as a percentage of t

c(OSCCLK)

45

55

%

C12

t

w(CIH)

Pulse duration, XCLKIN high as a percentage of t

c(OSCCLK)

45

55

%

(1)

This applies to the X1 pin also.

Table 6-10. XCLKIN

(1)

Timing Requirements - PLL Disabled

NO.

MIN

MAX

UNIT

C8

t

c(CI)

Cycle time, XCLKIN

100-MHz device

10

250

ns

60-MHz device

16.67

250

C9

t

f(CI)

Fall time, XCLKIN

Up to 20 MHz

6

ns

20 MHz to 100 MHz

2

ns

C10

t

r(CI)

Rise time, XCLKIN

Up to 20 MHz

6

ns

20 MHz to 100 MHz

2

ns

C11

t

w(CIL)

Pulse duration, XCLKIN low as a percentage of t

c(OSCCLK)

45

55

%

C12

t

w(CIH)

Pulse duration, XCLKIN high as a percentage of t

c(OSCCLK)

45

55

%

(1)

This applies to the X1 pin also.

The possible configuration modes are shown in

.

Table 6-11. XCLKOUT Switching Characteristics (PLL Bypassed or Enabled)

(1) (2)

NO.

PARAMETER

MIN

TYP

MAX

UNIT

100-MHz device

10

C1

t

c(XCO)

Cycle time, XCLKOUT

ns

60-MHz device

16.67

C3

t

f(XCO)

Fall time, XCLKOUT

2

ns

C4

t

r(XCO)

Rise time, XCLKOUT

2

ns

C5

t

w(XCOL)

Pulse duration, XCLKOUT low

H – 2

H + 2

ns

C6

t

w(XCOH)

Pulse duration, XCLKOUT high

H – 2

H + 2

ns

t

p

PLL lock time

131072t

c(OSCCLK)

(3)

cycles

(1)

A load of 40 pF is assumed for these parameters.

(2)

H = 0.5t

c(XCO)

(3)

OSCCLK is either the output of the on-chip oscillator or the output from an external oscillator.

Copyright © 2003–2012, Texas Instruments Incorporated

Electrical Specifications

105

Product Folder Link(s):