Texas Instruments TMS320F2802 User Manual

Page 74

LSPCLK

Frame Format and Mode

Even/Odd

Enable

Parity

8

SCIRXD

SCIRXST.1

TXENA

RXWAKE

SCITXD

SCICCR.6 SCICCR.5

RXSHF Register

SCITXD

TXSHF

Register

WUT

SCICTL1.3

TXWAKE

1

Baud Rate

MSbyte

Register

Baud Rate

LSbyte

Register

SCIHBAUD. 15 - 8

SCILBAUD. 7 - 0

TX

FIFO

Interrupts

RXENA

SCICTL1.0

RX

FIFO

Interrupts

SCICTL1.1

SCIRXD

RX ERR INT ENA

SCICTL1.6

RX Error

PE

FE OE

RX Error

SCIRXST.7

SCIRXST.4 - 2

8

SCITXBUF.7-0

TX FIFO Registers

Transmitter-Data

Buffer Register

8

SCIFFENA

TX FIFO _15

- - - - -

TX FIFO _1

TX FIFO _0

SCIFFTX.14

SCIRXBUF.7-0

RX FIFO Registers

Receive-Data

Buffer Register

SCIRXBUF.7-0

8

SCIFFRX.15

RXFFOVF

RX FIFO _0

- - - - -

RX FIFO _1

RX FIFO _15

SCI TX Interrupt Select Logic

TX EMPTY

SCICTL2.6

TXINT

TXRDY

SCICTL2.0

TX INT ENA

SCICTL2.7

To CPU

AutoBaud Detect Logic

TX Interrupt Logic

RX Interrupt Logic

SCI RX Interrupt Select Logic

RXRDY

SCIRXST.6

BRKDT

SCIRXST.5

RX/BK INT ENA

SCICTL2.1

RXINT

To CPU

, , ,

SPRS230N – OCTOBER 2003 – REVISED MAY 2012

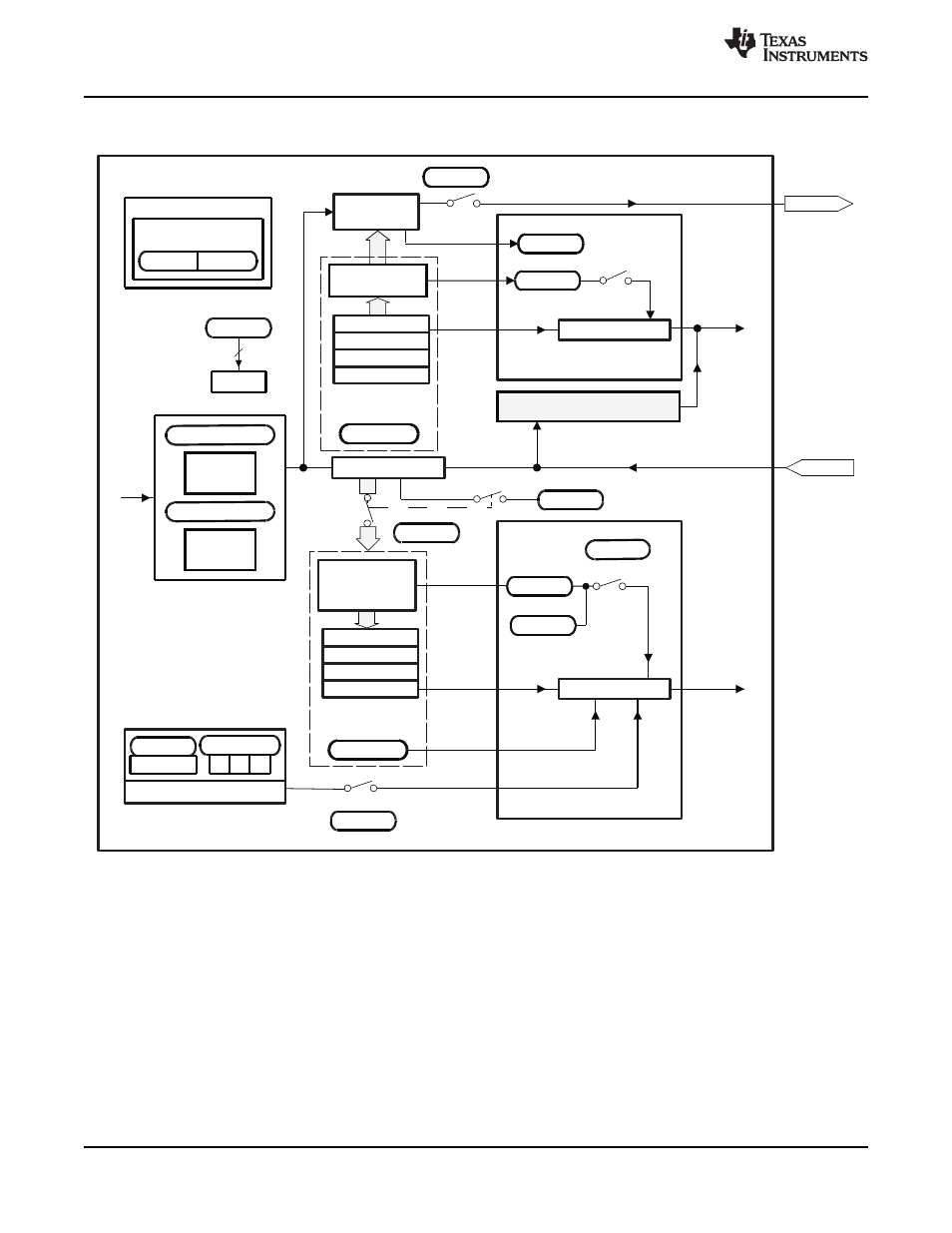

shows the SCI module block diagram.

Figure 4-13. Serial Communications Interface (SCI) Module Block Diagram

74

Peripherals

Copyright © 2003–2012, Texas Instruments Incorporated

Product Folder Link(s):