Texas Instruments TMS320F2802 User Manual

Page 80

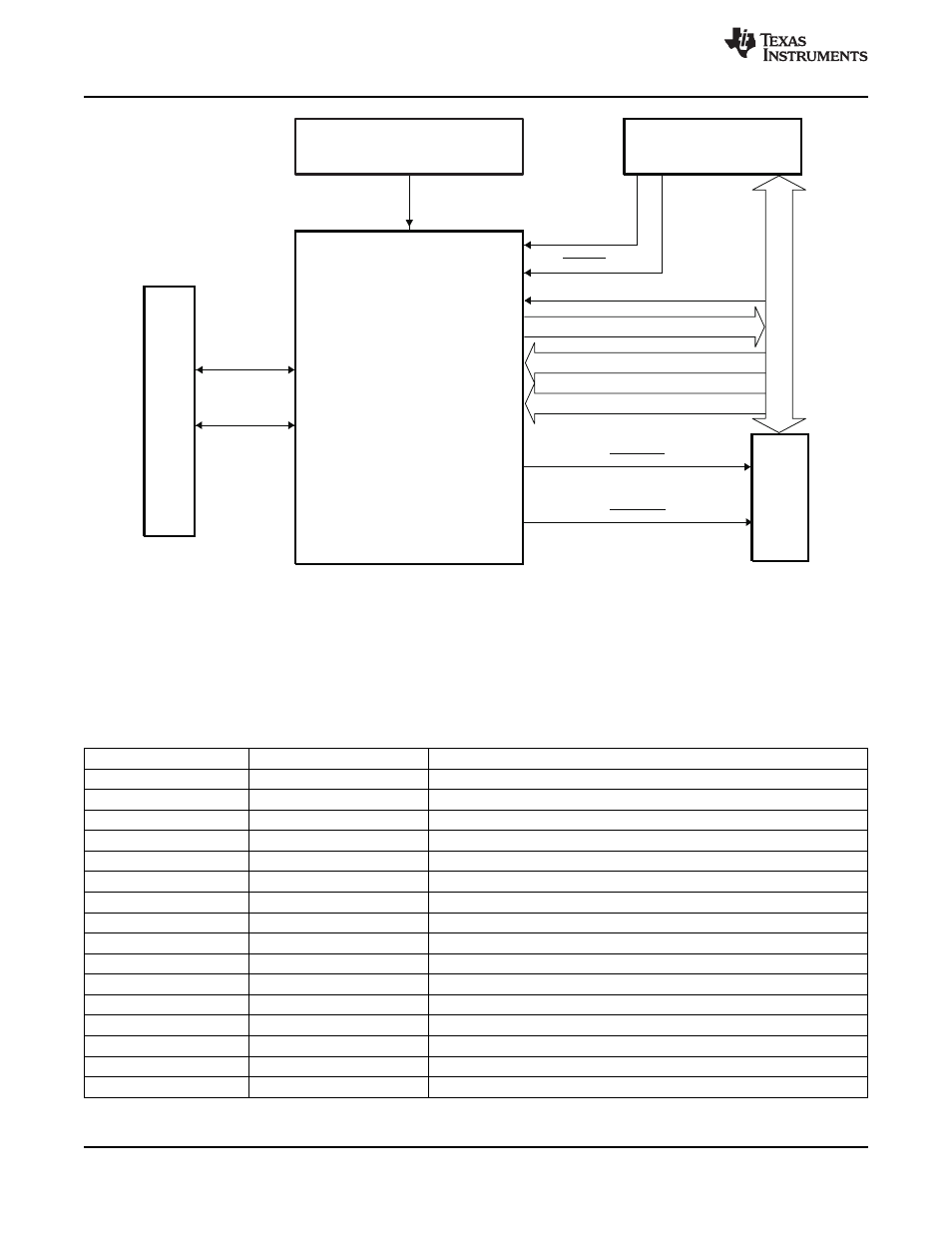

SYSRS

SYSCLKOUT

Control

I2CINT1A

I2CINT2A

C28x CPU

GPIO

MUX

Peripheral Bus

I2C-A

System Control Block

I2CAENCLK

PIE

Block

SDAA

SCLA

Data[16]

Data[16]

Addr[16]

, , ,

SPRS230N – OCTOBER 2003 – REVISED MAY 2012

A.

The I2C registers are accessed at the SYSCLKOUT rate. The internal timing and signal waveforms of the I2C port are

also at the SYSCLKOUT rate.

B.

The clock enable bit (I2CAENCLK) in the PCLKCRO register turns off the clock to the I2C port for low power

operation. Upon reset, I2CAENCLK is clear, which indicates the peripheral internal clocks are off.

Figure 4-15. I2C Peripheral Module Interfaces

The registers in

configure and control the I2C port operation.

Table 4-14. I2C-A Registers

NAME

ADDRESS

DESCRIPTION

I2COAR

0x7900

I2C own address register

I2CIER

0x7901

I2C interrupt enable register

I2CSTR

0x7902

I2C status register

I2CCLKL

0x7903

I2C clock low-time divider register

I2CCLKH

0x7904

I2C clock high-time divider register

I2CCNT

0x7905

I2C data count register

I2CDRR

0x7906

I2C data receive register

I2CSAR

0x7907

I2C slave address register

I2CDXR

0x7908

I2C data transmit register

I2CMDR

0x7909

I2C mode register

I2CISRC

0x790A

I2C interrupt source register

I2CPSC

0x790C

I2C prescaler register

I2CFFTX

0x7920

I2C FIFO transmit register

I2CFFRX

0x7921

I2C FIFO receive register

I2CRSR

-

I2C receive shift register (not accessible to the CPU)

I2CXSR

-

I2C transmit shift register (not accessible to the CPU)

80

Peripherals

Copyright © 2003–2012, Texas Instruments Incorporated

Product Folder Link(s):