Texas Instruments TMS320F2802 User Manual

Page 63

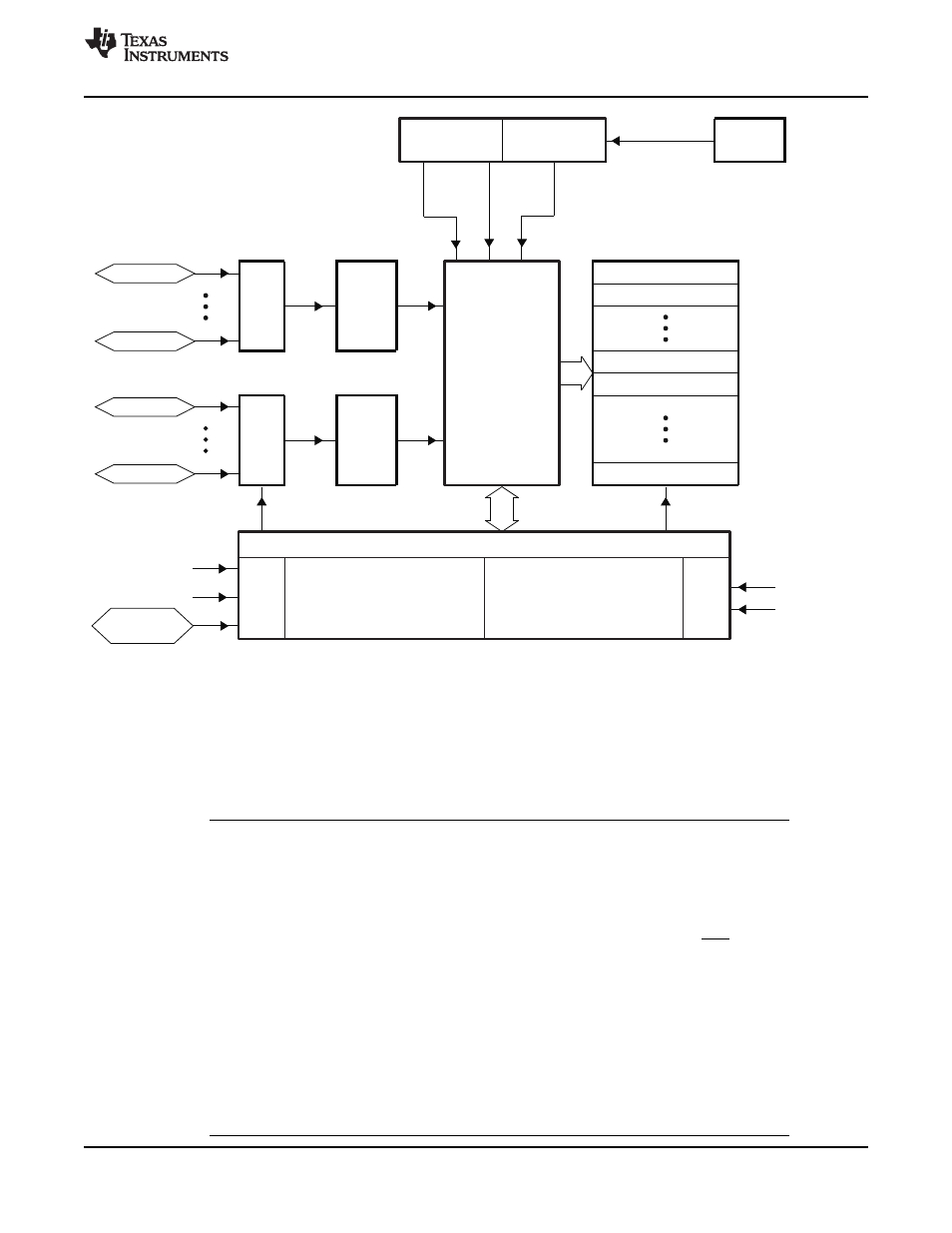

Result Registers

EPWMSOCB

S/W

ADC Control Registers

70B7h

70B0h

70AFh

70A8h

Result Reg 15

Result Reg 8

Result Reg 7

Result Reg 1

Result Reg 0

12-Bit

ADC

Module

Analog

MUX

EPWMSOCA

S/W

GPIO/XINT2_

ADCSOC

ADCINA0

ADCINA7

ADCINB0

ADCINB7

System

Control Block

High-Speed

Prescaler

HSPCLK

ADCENCLK

DSP

SYSCLKOUT

S/H

S/H

HALT

Sequencer 2

Sequencer 1

SOC

SOC

,

,

,

SPRS230N – OCTOBER 2003 – REVISED MAY 2012

Figure 4-7. Block Diagram of the ADC Module

To obtain the specified accuracy of the ADC, proper board layout is very critical. To the best extent

possible, traces leading to the ADCIN pins should not run in close proximity to the digital signal paths.

This is to minimize switching noise on the digital lines from getting coupled to the ADC inputs.

Furthermore, proper isolation techniques must be used to isolate the ADC module power pins (V

DD1A18

,

V

DD2A18

, V

DDA2

, V

DDAIO

) from the digital supply.

and

show the ADC pin connections

for the 280x devices.

NOTE

1. The ADC registers are accessed at the SYSCLKOUT rate. The internal timing of the

ADC module is controlled by the high-speed peripheral clock (HSPCLK).

2. The behavior of the ADC module based on the state of the ADCENCLK and HALT

signals is as follows:

–

ADCENCLK: On reset, this signal will be low. While reset is active-low (XRS) the

clock to the register will still function. This is necessary to make sure all registers and

modes go into their default reset state. The analog module, however, will be in a low-

power inactive state. As soon as reset goes high, then the clock to the registers will

be disabled. When the user sets the ADCENCLK signal high, then the clocks to the

registers will be enabled and the analog module will be enabled. There will be a

certain time delay (ms range) before the ADC is stable and can be used.

–

HALT: This mode only affects the analog module. It does not affect the registers. In

this mode, the ADC module goes into low-power mode. This mode also will stop the

clock to the CPU, which will stop the HSPCLK; therefore, the ADC register logic will

be turned off indirectly.

Copyright © 2003–2012, Texas Instruments Incorporated

Peripherals

63

Product Folder Link(s):