Table 2-3. signal descriptions (continued) – Texas Instruments TMS320F2802 User Manual

Page 20

, , ,

SPRS230N – OCTOBER 2003 – REVISED MAY 2012

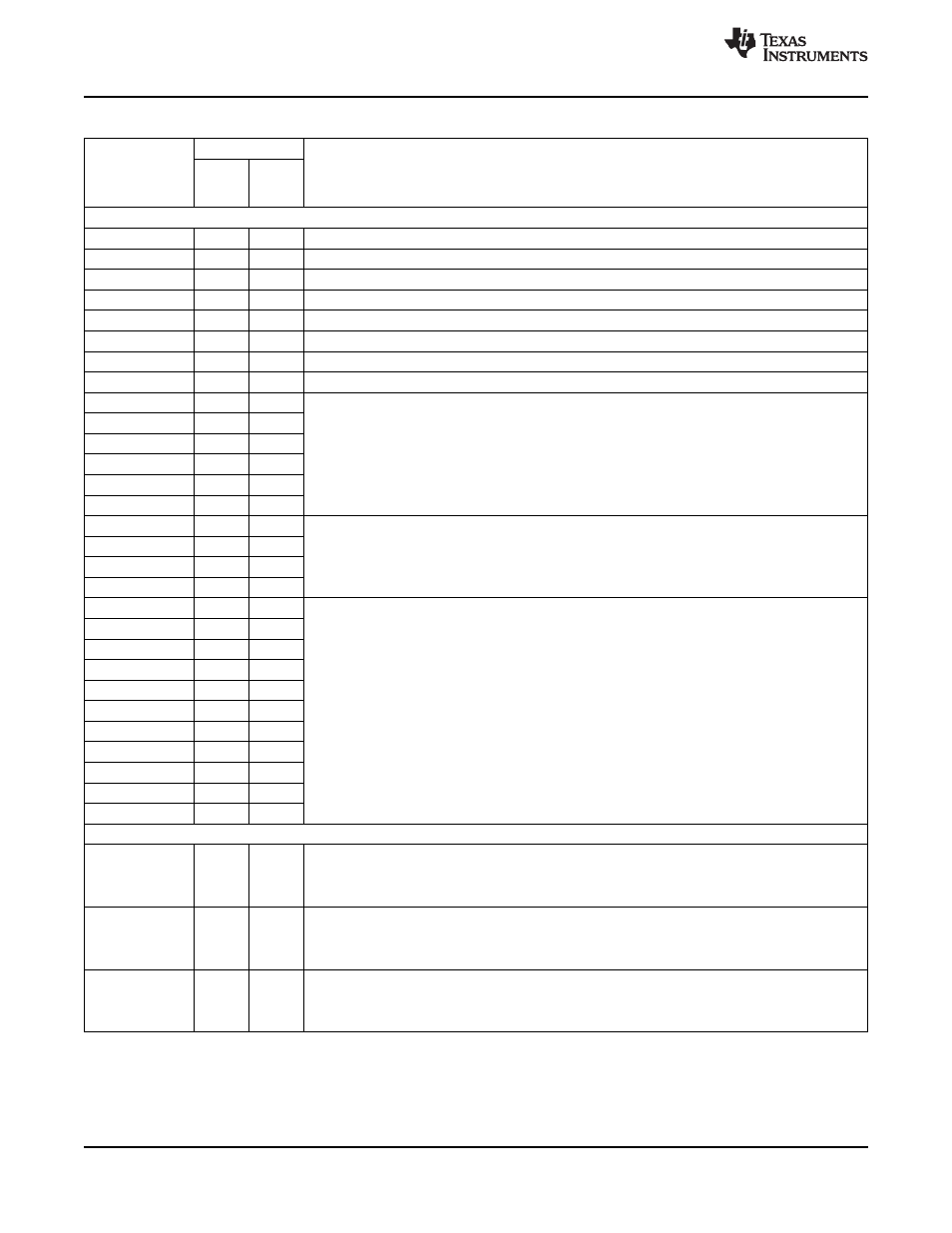

Table 2-3. Signal Descriptions (continued)

PIN NO.

GGM/

NAME

DESCRIPTION

(1)

PZ

ZGM

PIN #

BALL #

CPU AND I/O POWER PINS

V

DDA2

15

F2

ADC Analog Power Pin (3.3 V)

V

SSA2

14

F1

ADC Analog Ground Pin

V

DDAIO

26

J2

ADC Analog I/O Power Pin (3.3 V)

V

SSAIO

25

K1

ADC Analog I/O Ground Pin

V

DD1A18

12

E4

ADC Analog Power Pin (1.8 V)

V

SS1AGND

13

E5

ADC Analog Ground Pin

V

DD2A18

40

J6

ADC Analog Power Pin (1.8 V)

V

SS2AGND

39

K6

ADC Analog Ground Pin

V

DD

10

E2

V

DD

42

G6

V

DD

59

F10

CPU and Logic Digital Power Pins (1.8 V)

V

DD

68

D7

V

DD

85

B6

V

DD

93

D4

V

DDIO

3

C2

V

DDIO

46

H7

Digital I/O Power Pin (3.3 V)

V

DDIO

65

E9

V

DDIO

82

A7

V

SS

2

B1

V

SS

11

E3

V

SS

41

H6

V

SS

49

K9

V

SS

55

H10

V

SS

62

F7

Digital Ground Pins

V

SS

69

D10

V

SS

77

A9

V

SS

87

D6

V

SS

89

A5

V

SS

94

A4

GPIOA AND PERIPHERAL SIGNALS

(1) (2)

GPIO0

General-purpose input/output 0 (I/O/Z)

(3)

EPWM1A

Enhanced PWM1 Output A and HRPWM channel (O)

47

K8

-

-

-

-

GPIO1

General-purpose input/output 1 (I/O/Z)

(3)

EPWM1B

Enhanced PWM1 Output B (O)

44

K7

SPISIMOD

SPI-D slave in, master out (I/O) (not available on 2801, 2802)

-

-

GPIO2

General-purpose input/output 2 (I/O/Z)

(3)

EPWM2A

Enhanced PWM2 Output A and HRPWM channel (O)

45

J7

-

-

-

-

(1)

Some peripheral functions may not be available in TMS320F2801x devices. See

for details.

(2)

All GPIO pins are I/O/Z, 4-mA drive typical (unless otherwise indicated), and have an internal pullup, which can be selectively

enabled/disabled on a per-pin basis. This feature only applies to the GPIO pins. The GPIO function (shown in Italics) is the default at

reset. The peripheral signals that are listed under them are alternate functions.

(3)

The pullups on GPIO0-GPIO11 pins are not enabled at reset.

20

Introduction

Copyright © 2003–2012, Texas Instruments Incorporated

Product Folder Link(s):