Section 5.7 – Texas Instruments TMS320DM36X User Manual

Page 90

Ethernet Media Access Controller (EMAC) Registers

www.ti.com

5.7

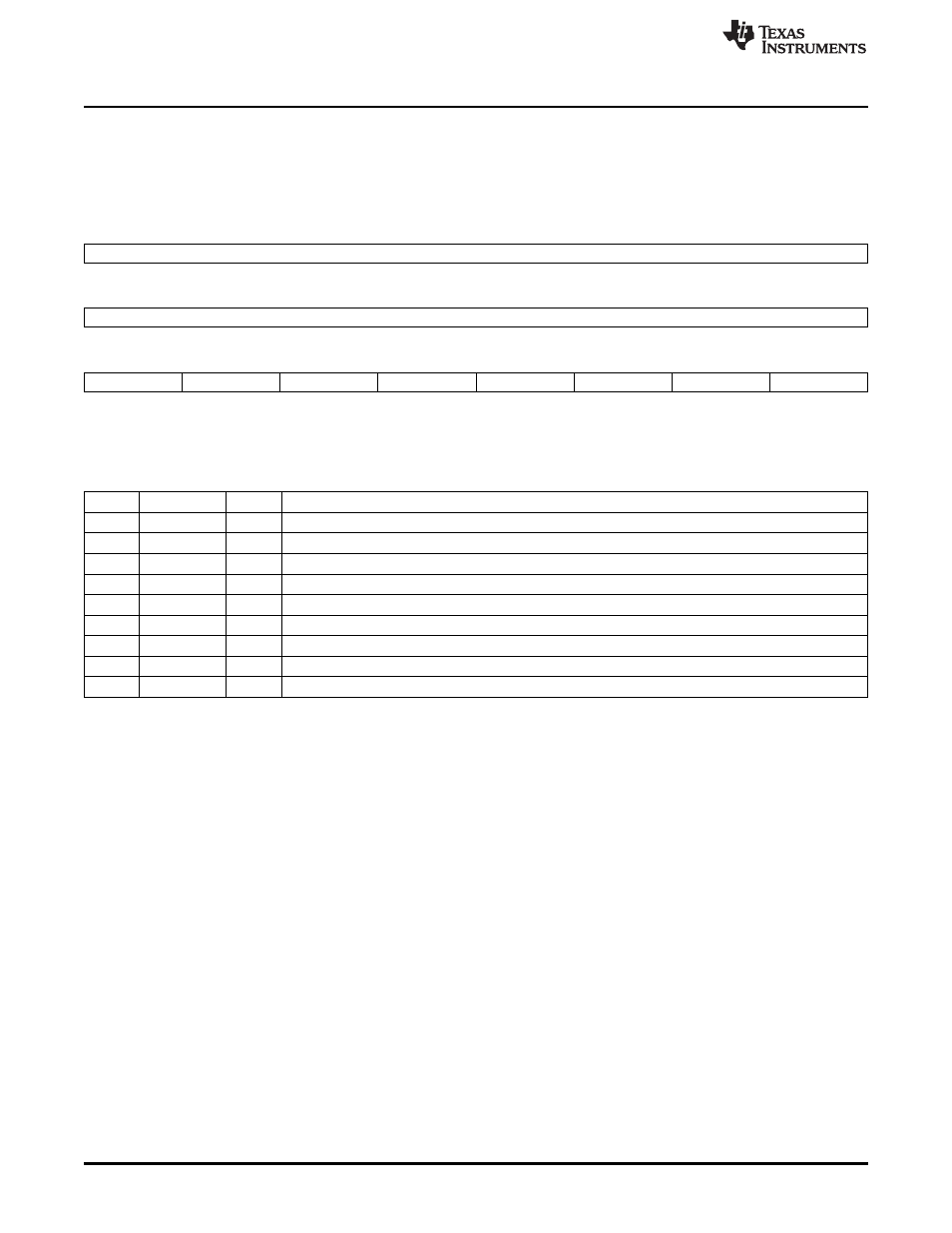

Transmit Interrupt Status (Unmasked) Register (TXINTSTATRAW)

The transmit interrupt status (unmasked) register (TXINTSTATRAW) is shown in

and

described in

.

Figure 46. Transmit Interrupt Status (Unmasked) Register (TXINTSTATRAW)

31

16

Reserved

R-0

15

8

Reserved

R-0

7

6

5

4

3

2

1

0

TX7PEND

TX6PEND

TX5PEND

TX4PEND

TX3PEND

TX2PEND

TX1PEND

TX0PEND

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

LEGEND: R = Read only; -n = value after reset

Table 44. Transmit Interrupt Status (Unmasked) Register (TXINTSTATRAW) Field Descriptions

Bit

Field

Value

Description

31-8

Reserved

0

Reserved

7

TX7PEND

0-1

TX7PEND raw interrupt read (before mask)

6

TX6PEND

0-1

TX6PEND raw interrupt read (before mask)

5

TX5PEND

0-1

TX5PEND raw interrupt read (before mask)

4

TX4PEND

0-1

TX4PEND raw interrupt read (before mask)

3

TX3PEND

0-1

TX3PEND raw interrupt read (before mask)

2

TX2PEND

0-1

TX2PEND raw interrupt read (before mask)

1

TX1PEND

0-1

TX1PEND raw interrupt read (before mask)

0

TX0PEND

0-1

TX0PEND raw interrupt read (before mask)

90

Ethernet Media Access Controller (EMAC)/Management Data Input/Output

SPRUFI5B – March 2009 – Revised December 2010

(MDIO)

© 2009–2010, Texas Instruments Incorporated