2 mdio control register (control), Section 4.2 – Texas Instruments TMS320DM36X User Manual

Page 71

www.ti.com

MDIO Registers

4.2

MDIO Control Register (CONTROL)

The MDIO control register (CONTROL) is shown in

and described in

.

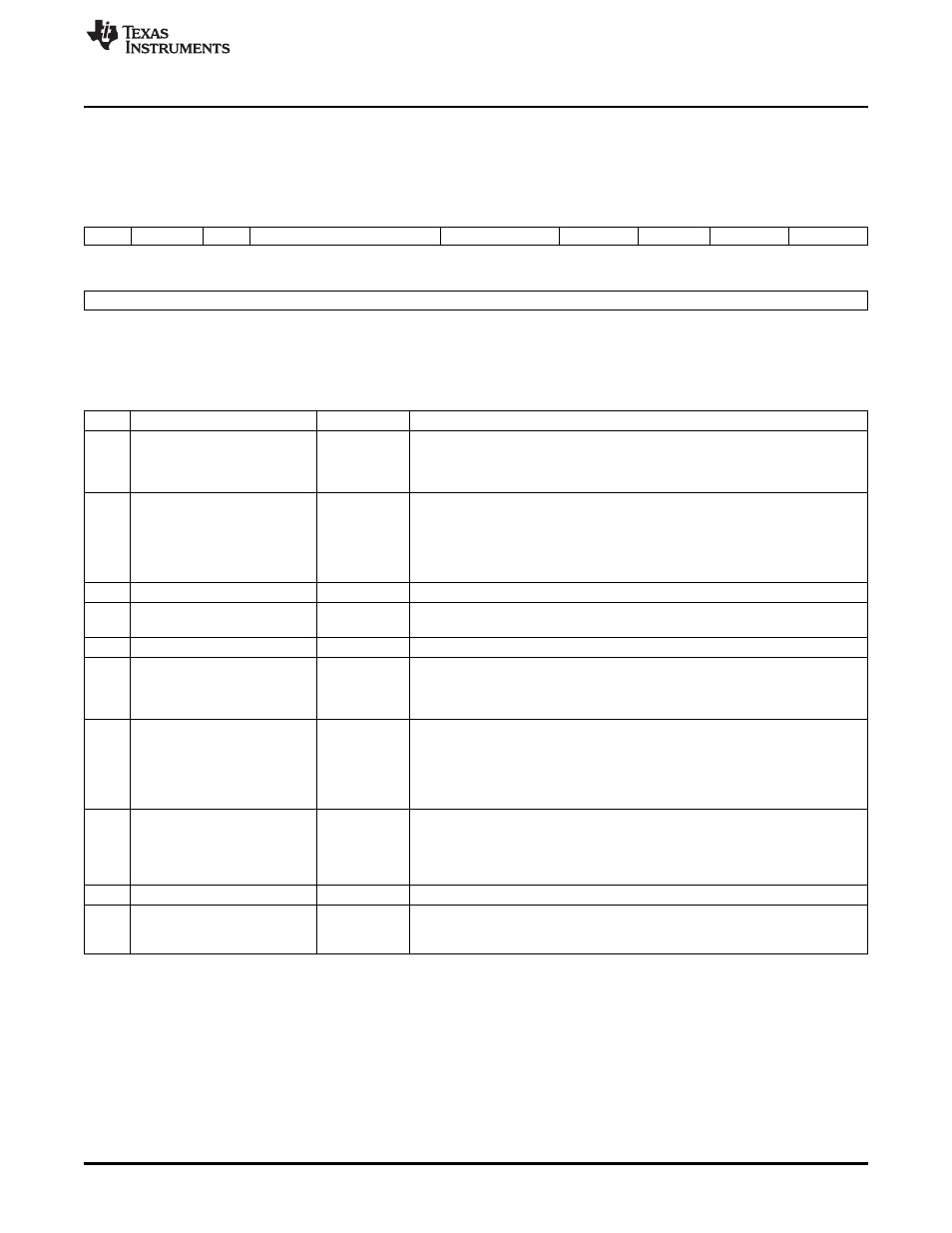

Figure 27. MDIO Control Register (CONTROL)

31

30

29

28

24

23

21

20

19

18

17

16

IDLE

ENABLE

Rsvd

HIGHEST_USER_CHANNEL

Reserved

PREAMBLE

FAULT

FAULTENB

Reserved

R-1

R/W-0

R-0

R-1

R-0

R/W-0

R/W1C-0

R/W-0

R-0

15

0

CLKDIV

R/W-FFh

LEGEND: R/W = R = Read only; R/W = Read/Write; W1C = Write 1 to clear, write of 0 has no effect; -n = value after reset

Table 24. MDIO Control Register (CONTROL) Field Descriptions

Bit

Field

Value

Description

31

IDLE

State machine IDLE status bit

0

State machine is not in idle state

1

State machine is in idle state

30

ENABLE

State machine enable control bit. If the MDIO state machine is active at the time

it is disabled, it will complete the current operation before halting and setting the

idle bit.

0

Disables the MDIO state machine

1

Enable the MDIO state machine

29

Reserved

0

Reserved

28-24

HIGHEST_USER_CHANNEL

0-1Fh

Highest user channel that is available in the module. It is currently set to 1. This

implies that MDIOUserAccess1 is the highest available user access channel.

23-21

Reserved

0

Reserved

20

PREAMBLE

Preamble disable

0

Standard MDIO preamble is used

1

Disables this device from sending MDIO frame preambles

19

FAULT

Fault indicator. This bit is set to 1 if the MDIO pins fail to read back what the

device is driving onto them. This indicates a physical layer fault and the module

state machine is reset. Writing a 1 to it clears this bit, writing a 0 has no effect.

0

No failure

1

Physical layer fault; the MDIO state machine is reset

18

FAULTENB

Fault detect enable. This bit has to be set to 1 to enable the physical layer fault

detection.

0

Disables the physical layer fault detection

1

Enables the physical layer fault detection

17-16

Reserved

0

Reserved

15-0

CLKDIV

0-FFFFh

Clock Divider bits. This field specifies the division ratio between the peripheral

clock and the frequency of MDCLK. MDCLK is disabled when CLKDIV is set to

0. MDCLK frequency = peripheral clock frequency/(CLKDIV + 1).

71

SPRUFI5B – March 2009 – Revised December 2010

Ethernet Media Access Controller (EMAC)/Management Data Input/Output

(MDIO)

© 2009–2010, Texas Instruments Incorporated