31 emulation control register (emcontrol), 32 fifo control register (fifocontrol), Section 5.31 – Texas Instruments TMS320DM36X User Manual

Page 113: Section 5.32

www.ti.com

Ethernet Media Access Controller (EMAC) Registers

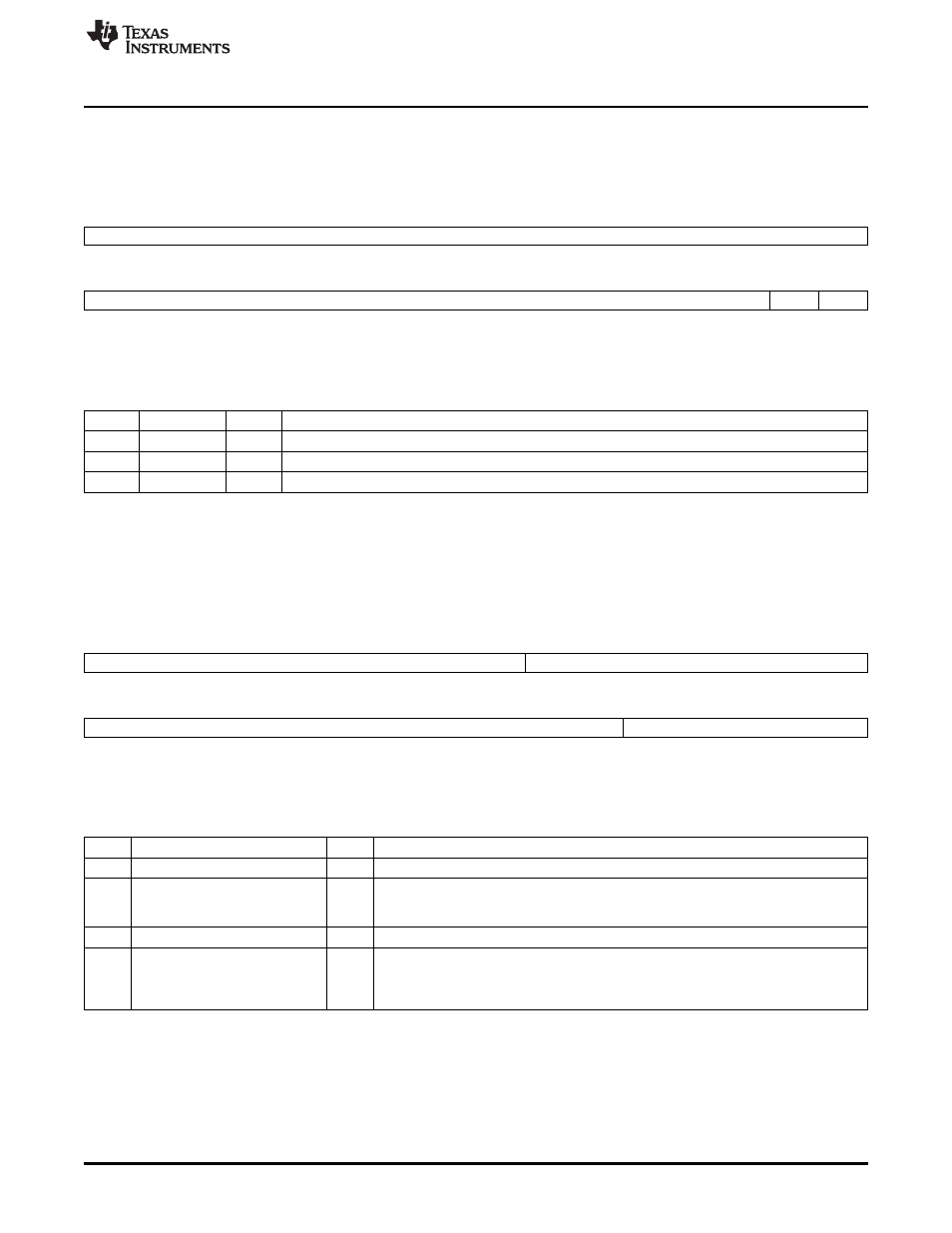

5.31 Emulation Control Register (EMCONTROL)

The emulation control register (EMCONTROL) is shown in

and described in

Figure 70. Emulation Control Register (EMCONTROL)

31

16

Reserved

R-0

15

2

1

0

Reserved

SOFT

FREE

R-0

R/W-0

R/W-0

LEGEND: R = Read only; R/W = Read/Write; -n = value after reset

Table 68. Emulation Control Register (EMCONTROL) Field Descriptions

Bit

Field

Value

Description

31-2

Reserved

0

Reserved

1

SOFT

0-1

Emulation soft bit

0

FREE

0-1

Emulation free bit

5.32 FIFO Control Register (FIFOCONTROL)

The FIFO control register (FIFOCONTROL) is shown in

and described in

Figure 71. FIFO Control Register (FIFOCONTROL)

31

23

22

16

Reserved

RXFIFOFLOWTHRESH

R-0

R/W-2h

15

5

4

0

Reserved

TXCELLTHRESH

R-0

R/W-18h

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 69. FIFO Control Register (FIFOCONTROL) Field Descriptions

Bit

Field

Value

Description

31-23

Reserved

0

Reserved

22-16

RXFIFOFLOWTHRESH

0-3Fh

Receive FIFO flow control threshold. Occupancy of the receive FIFO when receive

FIFO flow control is triggered (if enabled). The default value is 2h, which means that

receive FIFO flow control is triggered when the occupancy of the FIFO reaches 2 cells.

15-5

Reserved

0

Reserved

4-0

TXCELLTHRESH

0-1Fh

Transmit FIFO cell threshold. Indicates the number of 64-byte packet cells required to

be in the transmit FIFO before the packet transfer is initiated. Packets with fewer cells

are initiated when the complete packet is contained in the FIFO. This value must be

greater than or equal to 2 and less than or equal to 24 (2

≥

TXCELLTHRESH

≤

24).

113

SPRUFI5B – March 2009 – Revised December 2010

Ethernet Media Access Controller (EMAC)/Management Data Input/Output

(MDIO)

© 2009–2010, Texas Instruments Incorporated