9 emac module, 1 emac module components, 1 receive dma engine – Texas Instruments TMS320DM36X User Manual

Page 37: 2 receive fifo

Clock and

reset logic

Receive

DMA engine

Interrupt

controller

Transmit

DMA engine

Control

registers

Configuration bus

EMAC

control

module

Configuration bus

RAM

State

FIFO

Receive

FIFO

Transmit

MAC

transmitter

Statistics

receiver

MAC

SYNC

www.ti.com

Architecture

2.9

EMAC Module

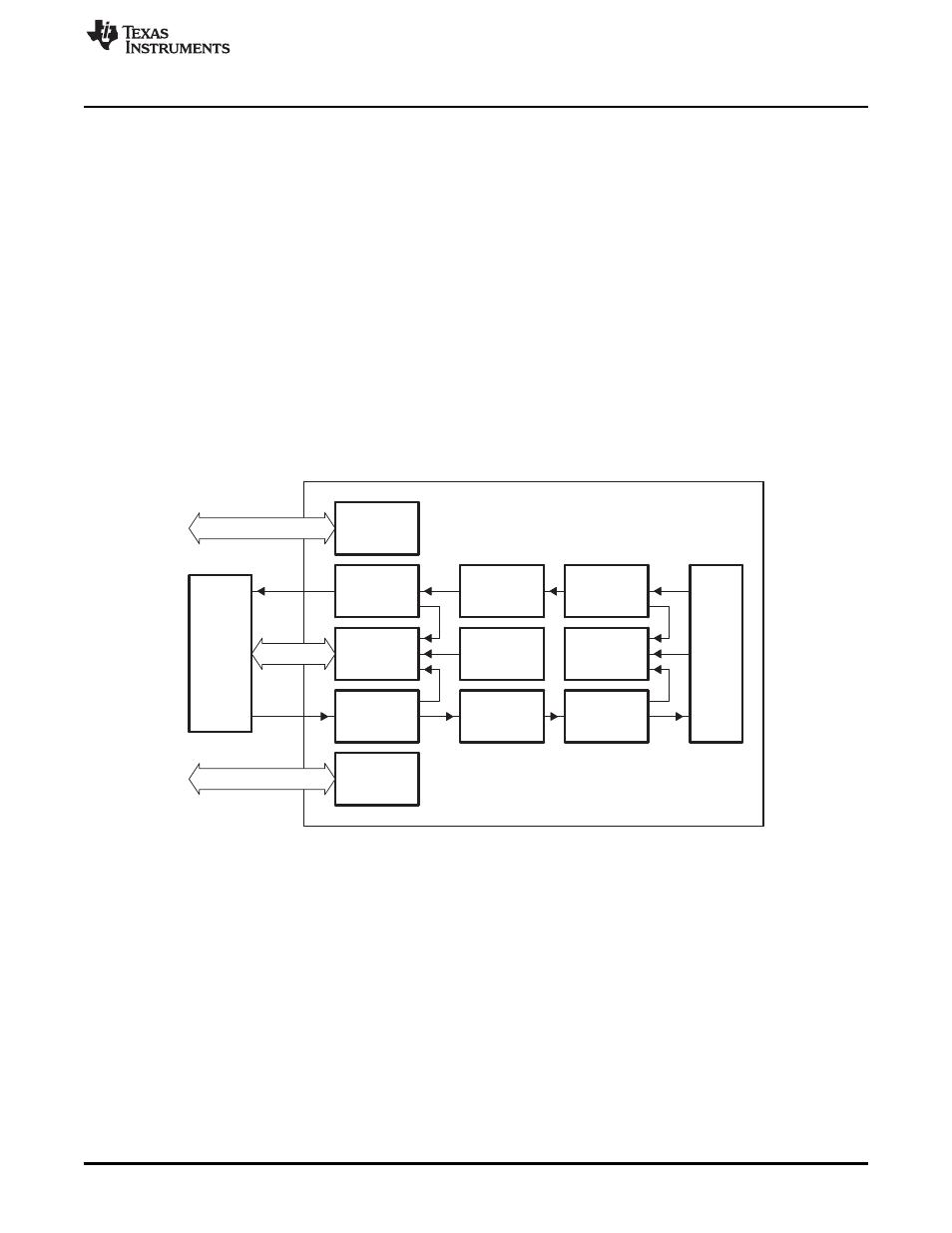

This section discusses the architecture and basic function of the EMAC module.

2.9.1

EMAC Module Components

The EMAC module (

) interfaces to the outside world through the Media Independent Interface

(MII) and interfaces to the system core through the EMAC control module. The EMAC consists of the

following logical components:

•

The receive path includes: receive DMA engine, receive FIFO, and MAC receiver

•

The transmit path includes: transmit DMA engine, transmit FIFO, and MAC transmitter

•

Statistics logic

•

State RAM

•

Interrupt controller

•

Control registers and logic

•

Clock and reset logic

Figure 10. EMAC Module Block Diagram

2.9.1.1

Receive DMA Engine

The receive DMA engine is the interface between the receive FIFO and the system core. It interfaces to

the CPU through the bus arbiter in the EMAC control module. This DMA engine is totally independent of

the device DMA.

2.9.1.2

Receive FIFO

The receive FIFO consists of 68 cells of 64 bytes each and associated control logic. The FIFO buffers

receive data in preparation for writing into packet buffers in device memory, and also enable receive FIFO

flow control.

37

SPRUFI5B – March 2009 – Revised December 2010

Ethernet Media Access Controller (EMAC)/Management Data Input/Output

(MDIO)

© 2009–2010, Texas Instruments Incorporated