Section 3.7 – Texas Instruments TMS320DM36X User Manual

Page 64

EMAC Control Module Registers

www.ti.com

3.7

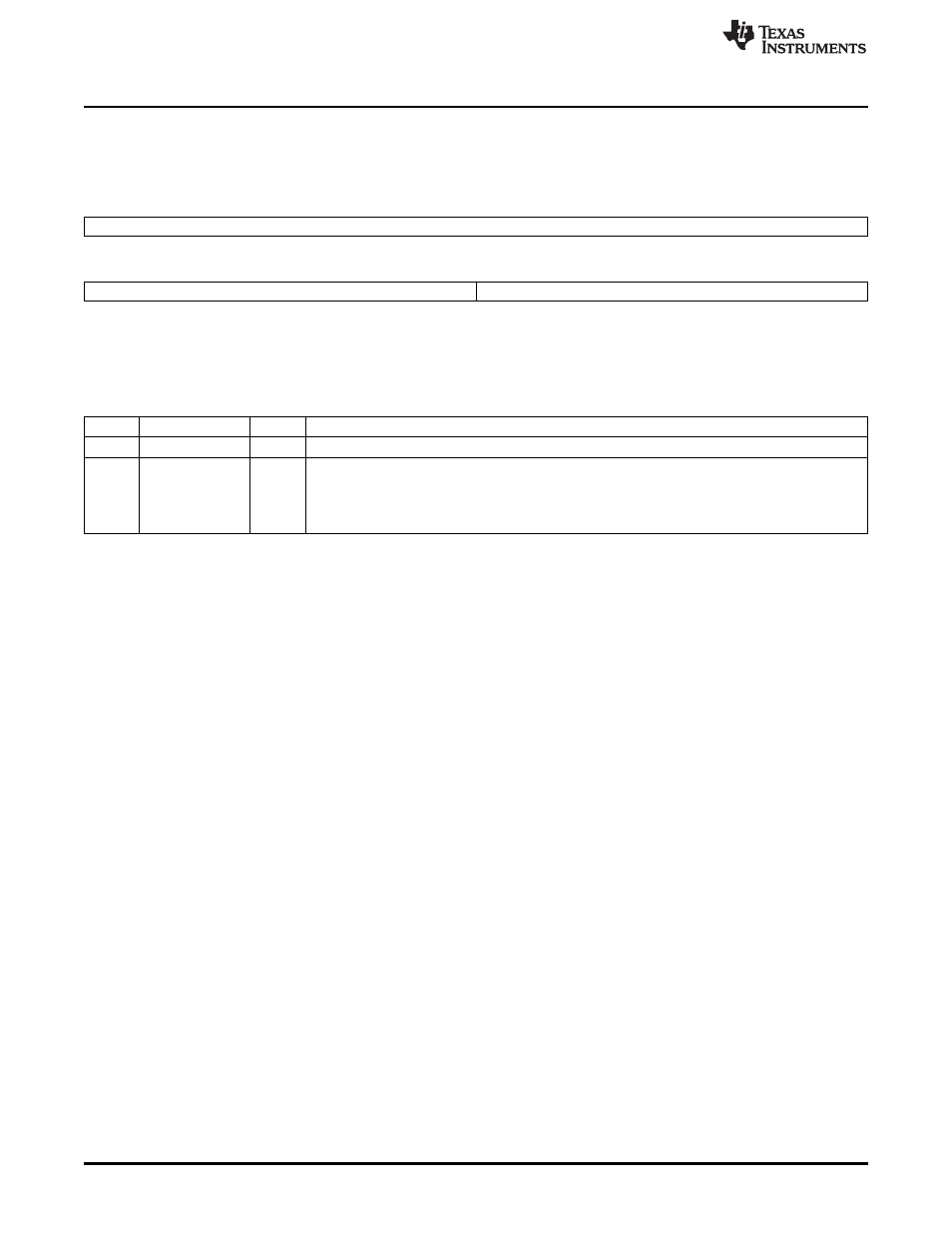

EMAC Control Module Transmit Interrupt Enable Register (CMTXINTEN)

The transmit interrupt enable register (CMTXINTEN) is shown in

and described in

Figure 18. EMAC Control Module Transmit Interrupt Enable Register (CMTXINTEN)

31

16

Reserved

R-0

15

8

7

0

Reserved

TXPULSEEN

R-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 14. EMAC Control Module Transmit Interrupt Enable Register (CMTXINTEN)

Field Descriptions

Bit

Field

Value

Description

31-8

Reserved

0

Reserved

7-0

TXPULSEEN[n]

Transmit interrupt (TXPENDn) enable. Each bit controls the corresponding channel n transmit

interrupt.

Bit n = 0,channel n transmit interrupt (TXPENDn) is disabled.

Bit n = 1, channel n transmit interrupt (TXPENDn) is enabled.

64

Ethernet Media Access Controller (EMAC)/Management Data Input/Output

SPRUFI5B – March 2009 – Revised December 2010

(MDIO)

© 2009–2010, Texas Instruments Incorporated

- Digital Signal Processor SM320F2812-HT (153 pages)

- MSP430x1xx (440 pages)

- Laser And Motor Drives DRV8811EVM (13 pages)

- TMS320 DSP (88 pages)

- MSP430x11x1 (45 pages)

- TVP5154EVM (55 pages)

- TMS320DM646X DMSOC (64 pages)

- CC2511 (24 pages)

- SN65HVS880 (4 pages)

- TPS650231EVM (14 pages)

- TMS320TCI648x (256 pages)

- TSC2007EVM-PDK (16 pages)

- UCC38500EVM (16 pages)

- TMS320C6000 (62 pages)

- SCAU020 (21 pages)

- TPS40051 (17 pages)

- TNETE2201 (14 pages)

- TMS320C64x DSP (306 pages)

- UCC2891 (21 pages)

- TMS320C3x (757 pages)

- MSP430 (138 pages)

- TMS320C6712D (102 pages)

- MSP430x4xx (512 pages)

- TMS320C6454 (225 pages)

- SPRU938B (48 pages)

- TUSB3210 (22 pages)

- TMS320C6457 (43 pages)

- CC2530ZNP (3 pages)

- TMS320C6455 (50 pages)

- TSB12LV26 (91 pages)

- TMS320C6472 (2 pages)

- VLYNQ Port (49 pages)

- TMS380C26 (92 pages)

- MSP-FET430 (95 pages)

- TMS320TCI6486 (160 pages)

- TPS2330 (22 pages)

- DM648 DSP (47 pages)

- MSC1211 (35 pages)

- SPRAA56 (29 pages)

- DAC7741EVM (28 pages)

- CDCM7005 (34 pages)

- TMS370 (99 pages)

- Adpater (37 pages)

- TMS320C6452 DSP (46 pages)