5 receive control register (rxcontrol), 6 receive teardown register (rxteardown), Section 5.5 – Texas Instruments TMS320DM36X User Manual

Page 89: Section 5.6

www.ti.com

Ethernet Media Access Controller (EMAC) Registers

5.5

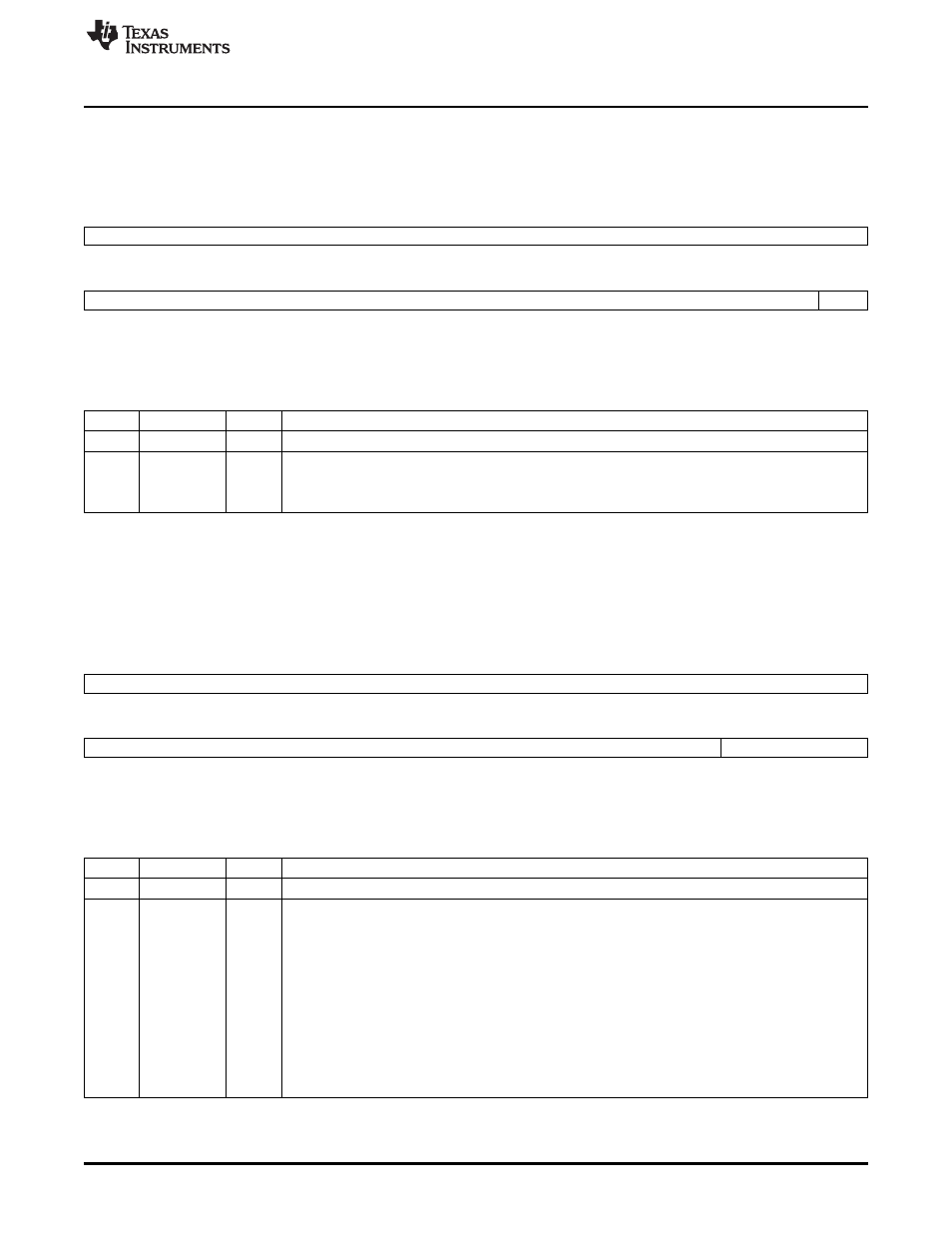

Receive Control Register (RXCONTROL)

The receive control register (RXCONTROL) is shown in

and described in

Figure 44. Receive Control Register (RXCONTROL)

31

16

Reserved

R-0

15

1

0

Reserved

RXEN

R-0

R/W-0

LEGEND: R = Read only; R/W = Read/Write; -n = value after reset

Table 42. Receive Control Register (RXCONTROL) Field Descriptions

Bit

Field

Value

Description

31-1

Reserved

0

Reserved

0

RXEN

Receive enable

0

Receive is disabled.

1

Receive is enabled.

5.6

Receive Teardown Register (RXTEARDOWN)

The receive teardown register (RXTEARDOWN) is shown in

and described in

Figure 45. Receive Teardown Register (RXTEARDOWN)

31

16

Reserved

R-0

15

3

2

0

Reserved

RXTDNCH

R-0

R/W-0

LEGEND: R = Read only; R/W = Read/Write; -n = value after reset

Table 43. Receive Teardown Register (RXTEARDOWN) Field Descriptions

Bit

Field

Value

Description

31-3

Reserved

0

Reserved

2-0

RXTDNCH

0-7h

Receive teardown channel. The receive channel teardown is commanded by writing the encoded value

of the receive channel to be torn down. The teardown register is read as 0.

0

Teardown receive channel 0

1h

Teardown receive channel 1

2h

Teardown receive channel 2

3h

Teardown receive channel 3

4h

Teardown receive channel 4

5h

Teardown receive channel 5

6h

Teardown receive channel 6

7h

Teardown receive channel 7

89

SPRUFI5B – March 2009 – Revised December 2010

Ethernet Media Access Controller (EMAC)/Management Data Input/Output

(MDIO)

© 2009–2010, Texas Instruments Incorporated