4 clock timing, 4 clock timing, Figure 4-1. mclk timing requirements – Rockwell SoniCrafter BT8960 User Manual

Page 84: Table 4-4, External clock timing requirements (mclk), Table 4-5, Hclk switching characteristics, Bt8960

74

4.0 Electrical & Mechanical Specifications

4.4 Clock Timing

Bt8960

Single-Chip 2B1Q Transceiver

N8960DSB

4.4 Clock Timing

Table 4-4. External Clock Timing Requirements (MCLK)

Symbol

Parameter

Minimum

Maximum

Units

1

MCLK Period (T

MCLK

)

(1)

75

196

ns

2

MCLK Pulse-Width Low

30

ns

3

MCLK Pulse-Width High

30

ns

Note:

(1). If an external clock is applied to XTALI/MCLK, it is referred to as MCLK.

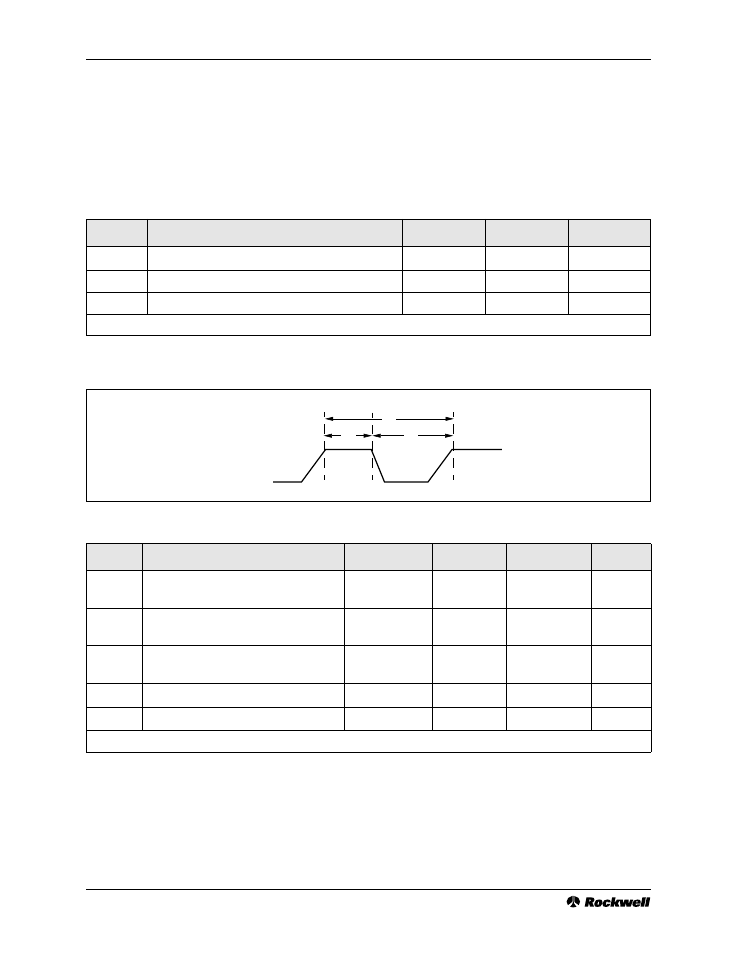

Figure 4-1. MCLK Timing Requirements

3

2

1

MCLK

Table 4-5. HCLK Switching Characteristics

Symbol

Parameter

Minimum

Typical

Maximum

Units

4

HCLK Period (T

HCLK

), hclk_freq[1:0] = ‘00’

or ‘11’ (N=6)

(1)

T

QCLK

÷

64

T

QCLK

÷

64

T

QCLK

÷

64

5

HCLK Period (T

HCLK

), hclk_freq[1:0] = ‘01’

(N=2)

(1)

T

QCLK

÷

16

T

QCLK

÷

16

T

QCLK

÷

16

6

HCLK Period (T

HCLK

), hclk_freq[1:0] = ‘10’

(N=4)

(1)

T

QCLK

÷

32

T

QCLK

÷

32

T

QCLK

÷

32

7

HCLK Pulse-Width High

T

HCLK

÷

2 – 10

T

HCLK

÷

2

T

HCLK

÷

2 + 10

ns

8

HCLK Pulse-Width Low

T

HCLK

÷

2 – 10

T

HCLK

÷

2

T

HCLK

÷

2 + 10

ns

Notes: (1). The hclk_freq[1:0] control bits are located in the Serial Monitor Source Select Register [addr. 0x01].