6 test and diagnostic interface (jtag), 6 test and diagnostic interface (jtag), Table 2-8 – Rockwell SoniCrafter BT8960 User Manual

Page 46: Device identification jtag register

36

2.0 Functional Description

2.6 Test and Diagnostic Interface (JTAG)

Bt8960

Single-Chip 2B1Q Transceiver

N8960DSB

2.6 Test and Diagnostic Interface (JTAG)

As the complexity of communications chips increases, the need to easily access

individual chips for PCB verification is becoming vital. As a result, special cir-

cuitry has been incorporated within the transceiver which complies fully with

IEEE standard 1149.1-1990, “Standard Test Access Port and Boundary Scan

Architecture” set by the Joint Test Action Group.

JTAG has four dedicated pins that comprise the Test Access Port (TAP): Test

Mode Select (TMS), Test Clock (TCK), Test Data Input (TDI), and Test Data Out

(TDO). Verification of the integrated circuit and its connection to other modules

on the printed circuit board can be achieved through these four TAP pins.

JTAG’s approach to testability utilizes boundary scan cells placed at each dig-

ital pin, both inputs and outputs. All scan cells are interconnected into a bound-

ary-scan register which applies or captures test data used for functional

verification of the PC board interconnection. JTAG is particularly useful for board

testers using functional testing methods.

With boundary-scan cells at each digital pin, the ability to apply and capture

the respective logic levels is provided. Since all of the digital pins are intercon-

nected as a long shift register, the TAP logic has access and control of all neces-

sary pins to verify functionality. For mixed signal ICs, the chip boundary

definition is expanded to include the on-chip interface between digital and analog

circuitry. Internal supply monitor circuitry ensures that each pin is initialized to

operate as an 2B1Q transceiver, instead of JTAG test mode during a power-up

sequence.

The JTAG standard defines an optional device identification register. This reg-

ister is included and contains a revision number, a part number, and a manufactur-

ers identification code specific to Rockwell. Access to this register is through the

TAP controller via the standard JTAG instruction set (see Table 2-8).

A variety of verification procedures can be performed through the TAP con-

troller. Board connectivity can be verified at all digital pins through a set of four

instructions accessible through the use of a state machine standard to all JTAG

controllers. Refer to the IEEE 1149.1 specification for details concerning the

Instruction Register and JTAG state machine. A Boundry Scan Description Lan-

guage (BSDL) file for the Bt8960 is also available from the factory upon request.

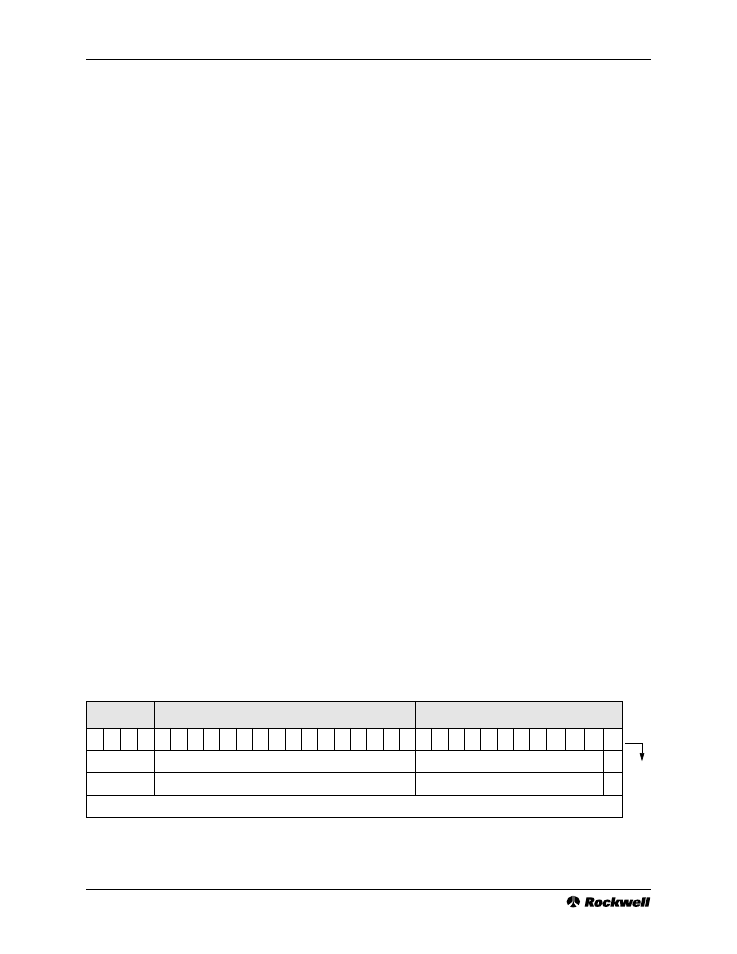

Table 2-8. JTAG Device Identification Register

Version

(1)

Part Number

Manufacturer ID

0

0

0

0

0

0

1

0

0

0

1

1

0

0

0

0

0

0

0

0

0

0

0

1

1

0

1

0

1

1

0

1

0x0

0x2300

0x0D6

4 bits

16 bits

11 bits

Notes: (1). Consult factory for current version number.

TDO