Bt8960 – Rockwell SoniCrafter BT8960 User Manual

Page 21

11

1.0 System Overview

1.3 Pin Descriptions

Bt8960

Single-Chip 2B1Q Transceiver

N8960DSB

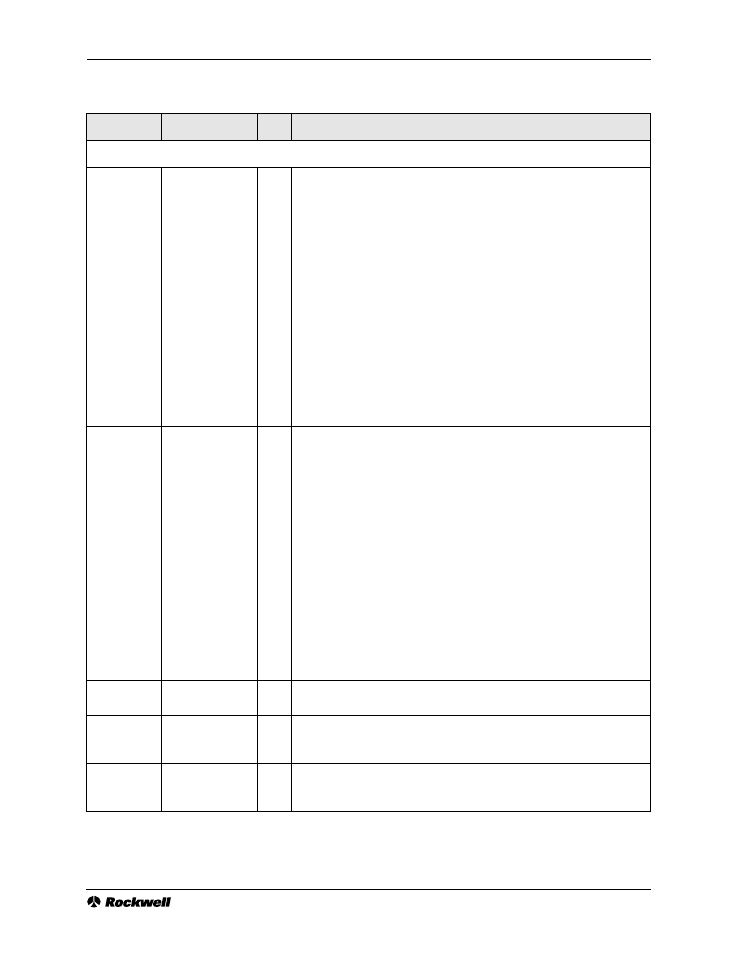

Channel Unit Interface

RQ[1]/

RDAT

RQ[0]/ BCLK

Receive Quat 1/

Receive Data

Receive Quat 0/

Bit Clock

O

O

RQ[1]/RDAT and RQ[0]/BCLK are bimodal outputs that represent the sign and

magnitude bits of the received quaternary output symbol in parallel channel unit

modes (RQ[1], RQ[0]), and the serial-data and bit-clock outputs in serial chan-

nel unit modes (RDAT, BCLK). Behavior of these outputs is configurable through

the Channel Unit Interface Modes Register [CU_interface_modes; 0x06] for par-

allel master, parallel slave, serial magnitude-bit-first and serial sign-bit-first

operations.

For parallel mode operation:

RQ[1] = Sign bit output

RQ[0] = Magnitude bit output

Both outputs are updated at the symbol rate on the rising edge of QCLK

(master mode) or the rising/falling edge (programmable) of RBCLK (slave

mode).

For serial mode operation:

RDAT = Serial quaternary data output

BCLK = Bit-rate (two times symbol rate) clock output

RDAT is updated at the bit rate on the rising edge of BCLK

TQ[1]/ TDAT

TQ[0]

Transmit Quat 1/

Transmit Data

Transmit Quat 0

I

I

TQ[1]/TDAT and TQ[0] are bimodal inputs that represent the sign and magnitude

bits of the quaternary input symbol to be transmitted in parallel channel unit

modes (TQ[1], TQ[0]), and the serial data input in serial channel unit modes

(TDAT). Interpretation of these inputs is configurable through the Channel Unit

Interface Modes Register [CU_Interface_modes; 0x06] for parallel master, par-

allel slave, serial magnitude-bit-first and serial sign-bit-first operations.

For parallel mode operation:

TQ[1] = Sign bit input

TQ[0] = Magnitude bit input

Both inputs are sampled at the symbol rate on the falling edge of QCLK (mas-

ter mode) or the rising/falling edge (programmable) of TBCLK (slave mode).

For serial mode operation:

TDAT = Serial quaternary data input

TQ0 = Don’t care (tie or pull up to supply rail)

TDAT is sampled at the bit rate (two times the symbol rate) on the falling

edge of BCLK.

QCLK

Quaternary Clock

O

Runs at the symbol rate. It defines the data on the TQ and RQ interfaces. QCLK

is also used to frame transmit/receive quats in serial mode.

TBCLK

Transmit Baud-

Rate Clock

I

Functions as the transmit baud-rate clock input. It must be frequency locked to

QCLK. This input is used only when the channel unit interface is in parallel slave

mode. If it is unused, it should be tied to VDD2 or DGND.

RBCLK

Receive Baud-

Rate Clock

I

Functions as the receive baud-rate clock input. It must be frequency locked to

QCLK. This input is used only when the channel unit interface is in parallel slave

mode. If it is unused, it should be tied to VDD2 or DGND.

Table 1-2. Hardware Signal Definitions (2 of 4)

Pin Label

Signal Name

I/O

Definition