55 0x5e, 0x5f— pll frequency register (pll_f, 56 0x70—lec read tap select register (linear, 57 0x71—lec write tap select register (linea – Rockwell SoniCrafter BT8960 User Manual

Page 77: 58 0x72—nec read tap select register (nonlin, 55 0x5e, 0x5f— pll frequency register, Pll_frequency_low, pll_frequency_high), Bt8960

67

3.0 Registers

3.1 Conventions

Bt8960

Single-Chip 2B1Q Transceiver

N8960DSB

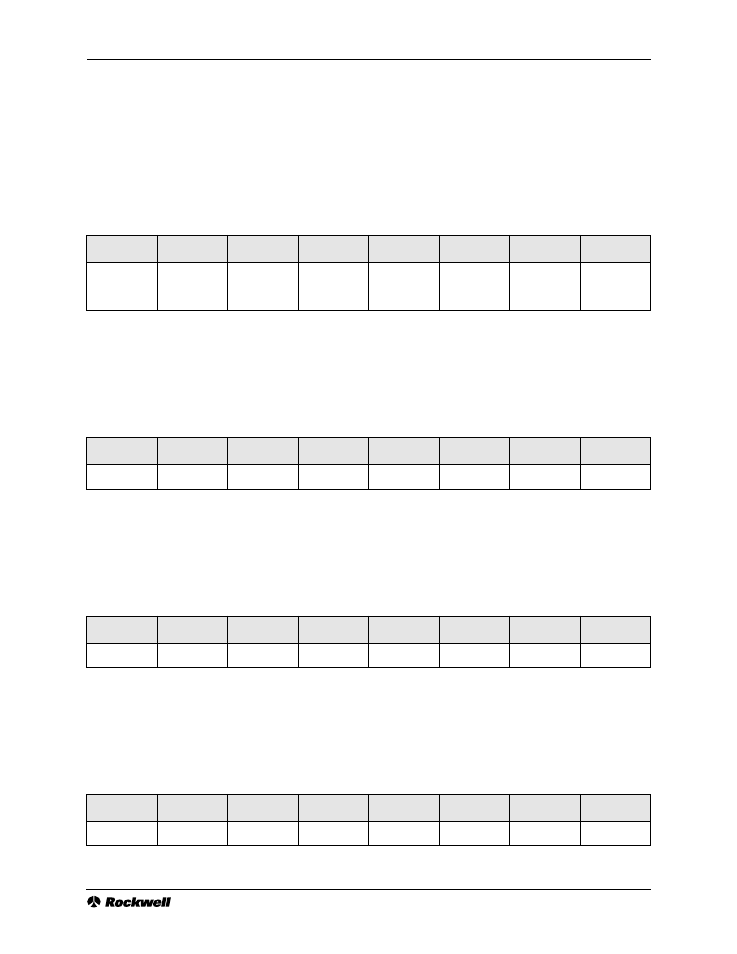

3.2.55 0x5E, 0x5F— PLL Frequency Register (pll_frequency_low,

pll_frequency_high)

A 2-byte read/write register comprising the 16 MSBs of the 31-bit, 2’s-complement timing recovery loop com-

pensation filter accumulator. Treated much like a meter register, the frequency register must be read low byte

first, followed by high byte, unseparated by any timing-function or meter-register read access. Writes must

occur in the same order, with the low byte written first, followed by the high byte. Write accesses may be sepa-

rated by any number of other read or write accesses.

3.2.56 0x70—LEC Read Tap Select Register (linear_ec_tap_select_read)

A 6-bit read/write register representing an unsigned binary address defined over a range of 0 to 59 decimals.

When written, it causes the selected 32-bit coefficient of the LEC to be subsequently loaded into the Access

Data Register [access_data_byte[3:0]; 0x7C–0x7F] within two symbol periods. Does not affect the value of the

coefficient.

3.2.57 0x71—LEC Write Tap Select Register (linear_ec_tap_select_write)

A 6-bit read/write register representing an unsigned binary address defined over a range of 0 to 59 decimals.

When written, it causes all 32 bits of the Access Data Register [access_data_byte[3:0]; 0x7C–0x7F] to be sub-

sequently written to the selected LEC coefficient within two symbol periods. Does not affect the value of the

access data register.

3.2.58 0x72—NEC Read Tap Select Register (nonlinear_ec_tap_select_read)

A 6-bit read/write register representing an unsigned binary address defined over a range of 0 to 63 decimals.

When written, it causes the selected 14-bit coefficient of the NEC to be subsequently loaded into the lowest-

order bits of the Access Data Register [access_data_byte[3:0]; 0x7C–0x7F] within two symbol periods. Does

not affect the value of the coefficient.

7

6

5

4

3

2

1

0

D[22]

D[21]

D[20]

D[19]

D[18]

D[17]

D[16]

D[15]

D[30]

D[29]

D[28]

D[27]

D[26]

D[25]

D[24]

D[23]

7

6

5

4

3

2

1

0

–

–

D[5]

D[4]

D[3]

D[2]

D[1]

D[0]

7

6

5

4

3

2

1

0

–

–

D[5]

D[4]

D[3]

D[2]

D[1]

D[0]

7

6

5

4

3

2

1

0

–

–

D[5]

D[4]

D[3]

D[2]

D[1]

D[0]