27 0x22—pll modes register (pll_modes), 27 0x22—pll modes register (pll_modes), Bt8960 – Rockwell SoniCrafter BT8960 User Manual

Page 66

56

3.0 Registers

3.1 Conventions

Bt8960

Single-Chip 2B1Q Transceiver

N8960DSB

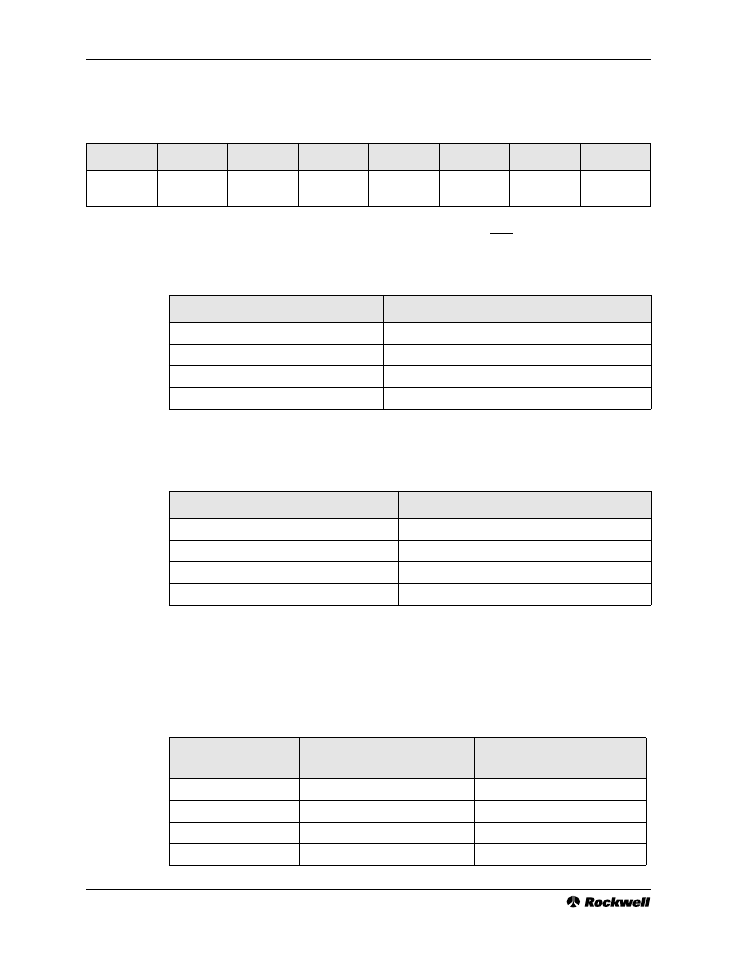

3.2.27 0x22—PLL Modes Register (pll_modes)

clk_freq[1,0]

Clock Frequency Select—Read/write binary field specifies one of four data rate ranges for

Bt8960 operation. The 00 state is automatically selected by RST assertion and upon initial

power application. The crystal or external clock frequency must be equal to 32 times the data

rate.

phase_detector_

gain[1,0]

Phase Detector Gain—Read/write binary field specifies one of four gain settings for the tim-

ing-recovery phase detector function.

freeze_pll

Freeze PLL—Read/write control bit. When set, this bit zeros the proportional term of the loop

compensation filter and disables accumulator updates causing the PLL to hold its current fre-

quency. When cleared, proportional term effects and accumulator updates are enabled allowing

the PLL to track the phase of the incoming data.

pll_gain[1,0]

PLL Gain—Read/write binary field specifies the gain (proportional and integral coefficients)

of the loop compensation filter.

7

6

5

4

3

2

1

0

clk_freq[1]

clk_freq[0]

negate_symbol

phase_detector_

gain[1]

phase_detector_

gain[0]

freeze_pll

pll_gain[1]

pll_gain[0]

clk_freq[1,0]

Range Data Rate

00

221 to 252kbps

01

Above 352 kbps

10

160 to 221 kbps

11

Reserved

phase_detector_gain[1,0]

Normalized Gain

00

1

01

2

10

4

11

Reserved

pll_gain[1:0]

Normalized

Proportional Coefficients

Normalized

Integral Coefficients

00

1

1

01

4

32

10

16

256

11

64

4096