8 0x07—receive phase select register (receiv, 9 0x08—linear echo canceller modes register, Bt8960 – Rockwell SoniCrafter BT8960 User Manual

Page 58

48

3.0 Registers

3.1 Conventions

Bt8960

Single-Chip 2B1Q Transceiver

N8960DSB

3.2.8 0x07—Receive Phase Select Register (receive_phase_select)

rphs[3:0]

Receive Phase Select—Read/write binary field that defines the relative phase relationship

between QCLK and the sampling point of the ADC. The rising edges of QCLK corresponds to

the ADC sampling point when rphs = 0000. Each binary increment of rphs represents a one-

sixteenth QCLK period delay in the sampling point relative to QCLK.

3.2.9 0x08—Linear Echo Canceller Modes Register (linear_ec_modes)

enable_dc_tap

Enable DC Tap—Read/write control bit which, when set, forces a constant +1 value into the

last data tap of the Linear Echo Canceller (LEC). This condition enables cancellation of any

residual DC offset present at the input to the LEC. When cleared, the last data tap operates nor-

mally, as the oldest transmit data sample.

adapt_coefficents

Adapt Coefficients—Read/write control bit which enables coefficient adaptation when set; dis-

ables/freezes adaptation when cleared. Coefficient values are preserved when adaptation is dis-

abled.

zero_coefficients

Zero Coefficients—Read/write control bit that continuously zeros all coefficients when set;

allows normal coefficient updates, if enabled, when cleared. This behavior differs slightly from

the similar function (zero_coefficients) of the FFE and EP filters.

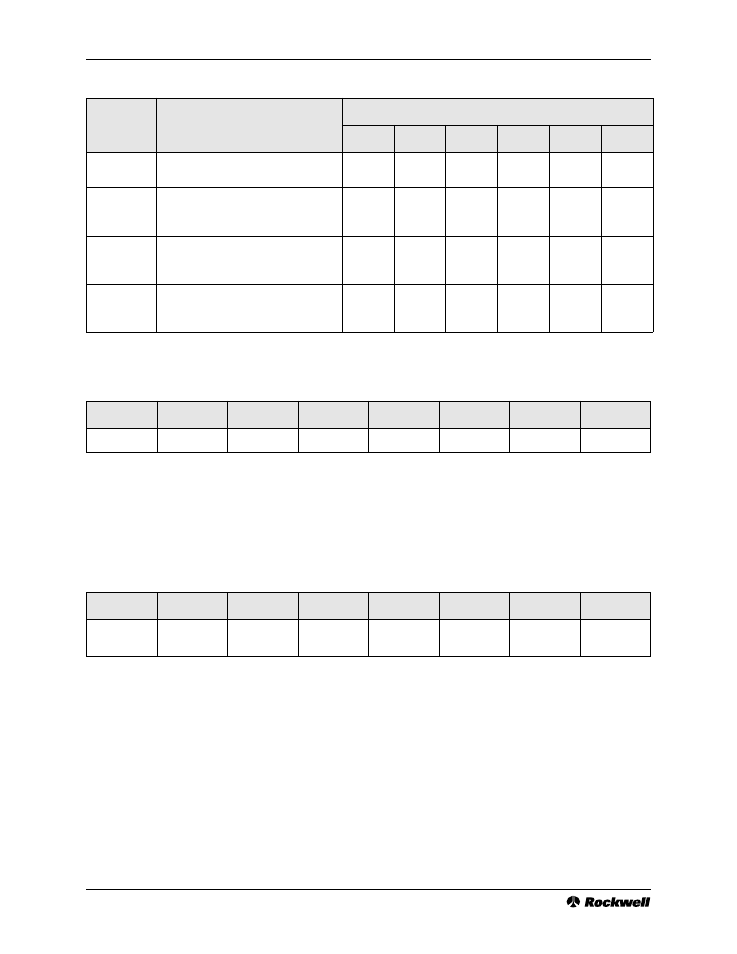

Interface

mode

[1:0]

Mode

Pin Functions

91

90

88

89

85

86

00

Parallel Master —Parallel quat transfer

synchronized to QCLK out.

Not

used

Not

used

RQ[1]

RQ[0]

TQ[1]

TQ[0]

01

Parallel Slave—Parallel quat transfer

synchronized to separate TBCLK and

RBCLK inputs.

TBCLK

RBCLK

RQ[1]

RQ[0]

TQ[1]

TQ[0]

10

Serial, Magnitude First. Serial quat

transfer synchronized to BCLK out;

magnitude-bit first followed by sign bit.

Not

used

Not

used

RDAT

BCLK

TDAT

Not

used

11

Serial, Sign First. Serial quat transfer

synchronized to BCLK out; sign-bit first

followed by magnitude bit.

Not

used

Not

used

RDAT

BCLK

TDAT

Not

used

7

6

5

4

3

2

1

0

–

–

–

–

rphs[3]

rphs[2]

rphs[1]

rphs[0]

7

6

5

4

3

2

1

0

–

–

enable_dc_tap

adapt_

coefficients

zero_coefficients

zero_output

adapt_gain[1]

adapt_gain[0]