41 0x3a—symbol detector modes register (dete – Rockwell SoniCrafter BT8960 User Manual

Page 71

61

3.0 Registers

3.1 Conventions

Bt8960

Single-Chip 2B1Q Transceiver

N8960DSB

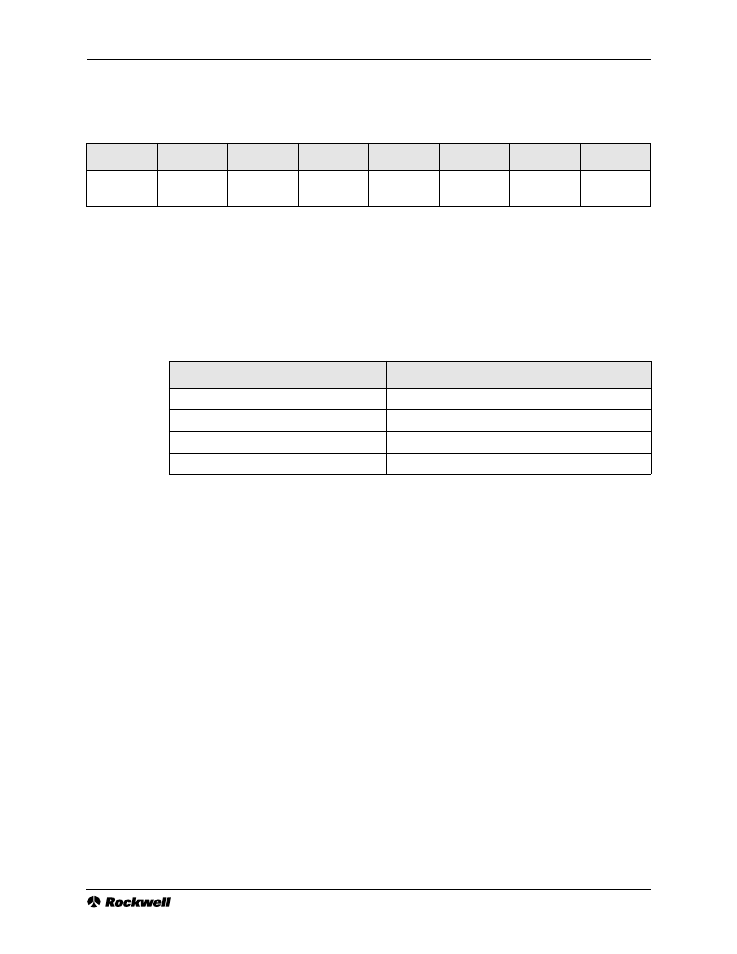

3.2.41 0x3A—Symbol Detector Modes Register (detector_modes)

enable_peak_

detector

Enable Peak Detector—Read/write control bit that enables the peak detection function when

set; disables the function when cleared. When enabled, the peak detector output overrides the

slicer output if the peak detection criteria are met. If the criteria are not met, or if the function

is disabled, the slicer output is used and peak detector output is ignored.

output_mux_

control[1,0]

Output Multiplexer Control—Read/write binary field that selects the source of the detector

output connected to the channel unit receive interface.

scr_out_to_dfe

Scrambler Output to DFE—Read/write control bit that selects the source of the detector output

connected to the DFE and timing recovery module inputs, and the transmitter’s detector loop-

back input. When set, this bit selects the scrambler/descrambler function; when cleared, it

selects the slicer/peak detector output.

two_level

Two-Level Mode—Read/write control bit that selects two-level mode when set, four-level

mode when cleared. Affects the slicer and the scrambler/descrambler function. In two-level

mode, the slicer uses a single threshold set at zero to recover sign bits only; all magnitude

information is lost. Scrambler/descrambler updates are slowed to the symbol rate (half the nor-

mal bit rate) to process only sign information as well; all magnitude output bits are sourced

with a constant logic zero value producing two-level symbols constrained to +3 and –3 values.

In 4-level mode, the slicer uses two thresholds derived from the Cursor Level Register

[cursor_level_low, cursor_level_high; 0x36–0x37], as well as the zero threshold, to recover

both sign and magnitude information. The scrambler/descrambler is updated at the full bit rate

to process both sign and magnitude bits as well.

lfsr_lock

LFSR Lock—Read/write control bit that enables the auto scrambler synchronization mode

(lfsr_lock) in the detector when set; disables this mode when cleared. Affects the behavior of

the scrambler/descrambler function, overriding the descr_on setting. When enabled, the

scrambler/descrambler is forced into the descrambler mode for 23 cycles. It is then switched to

the scrambled-ones mode for 128 cycles. While in this mode, the outputs of the scrambler and

the slicer/peak detector are compared against one another. The number of equivalent bits

(equal comparisons) is accumulated and compared to the value of the scrambler synchroniza-

tion threshold register [scr_sync_th; 0x2E].

At any time during the 128 cycles, if the count exceeds the threshold (greater than), the sync

interrupt flag is set in the IRQ Source Register [irq_source; 0x05] and the process terminates

with the scrambler/descrambler left in the scrambled-ones mode. (The sync interrupt flag can-

7

6

5

4

3

2

1

0

enable_peak_det

ector

output_mux_con

trol[1]

output_mux_con

trol[0]

scr_out_to_dfe

two_level

lfsr_lock

htur_lfsr

descr_on

output_mux_control[1,0]

Detector Output to CU Receive Interface

00

Same as scr_out_to_dfe selection.

01

Transmitter loopback output from CU transmit interface.

10

Scrambler/descrambler output.

11

Reserved.