3 programmable burst read latency operation, 3 handshaking operation, 4 output disable mode operation – Samsung MUXONENAND A-DIE KFM2G16Q2A User Manual

Page 95

MuxOneNAND2G(KFM2G16Q2A-DEBx)

- 95 -

FLASH MEMORY

MuxOneNAND4G(KFN4G16Q2A-DEBx)

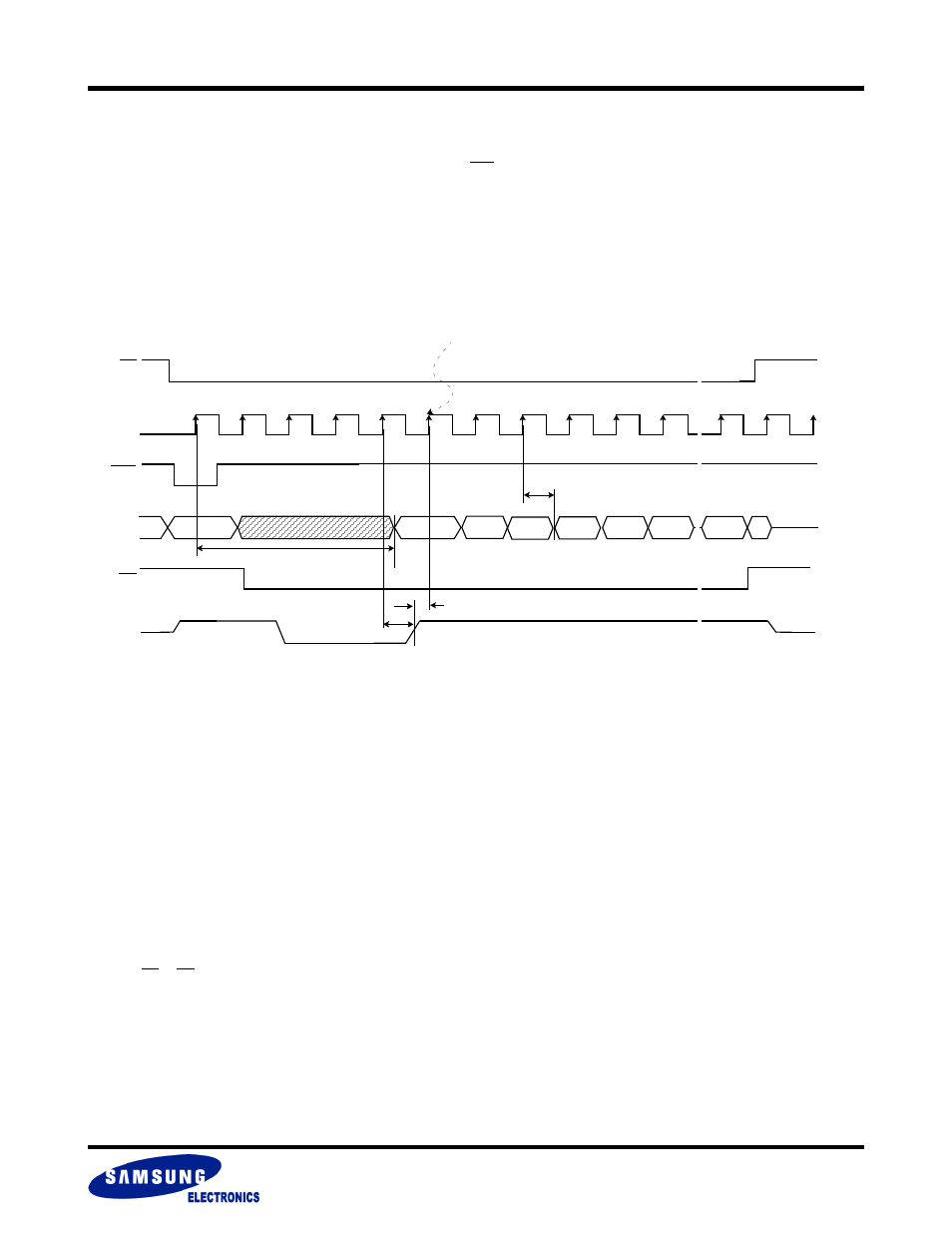

3.7.2.3 Programmable Burst Read Latency Operation

See Timing Diagrams 6.1 and 6.2

Upon power up, the number of initial clock cycles from Valid Address (AVD) to initial data defaults to four clocks.

The number of clock cycles (n) which are inserted after the clock which is latching the address. The host can read the first data with the

(n+1)th rising edge.

The number of total initial access cycles is programmable from three to seven cycles. After the number of programmed burst clock cycles is

reached, the rising edge of the next clock cycle triggers the next burst data.

Four Clock Burst Read Latency (BRWL=4 case)

*NOTE :

BRWL=4, HF=0 is recommended for 40MHz~66MHz. For frequency over 66MHz, BRWL should be 6 or 7 while HF=1.

Also, for frequency under 40MHz, BRWL can be reduced to 3, and HF=0.

3.7.3 Handshaking Operation

The handshaking feature allows the host system to simply monitor the RDY signal from the device to determine

when the initial word of burst data is ready to be read.

To set the number of initial cycles for optimal burst mode, the host should use the programmable burst read latency configuration (see Section

2.8.19, "System Configuration1 Register").

The rising edge of RDY which is derived at the same cycle of data fetch clock indicates the initial word of valid burst data.

3.7.4 Output Disable Mode Operation

When the CE or OE input is at V

IH

, output from the device is disabled.

The outputs are placed in the high impedance state.

t

IAA

Hi-Z

CE

CLK

AVD

OE

RDY

≈

≈

t

RDYA

A/DQ0:

A/DQ15

D6

D7

D0

D1

D2

D3

D7

D0

Hi-Z

≈

≈

≈

≈

Valid

Address

-1

0

1

2

3

t

BA

Rising edge of the clock cycle following last read latency

triggers next burst data

t

RDYS

4