17 cold reset timing – Samsung MUXONENAND A-DIE KFM2G16Q2A User Manual

Page 160

MuxOneNAND2G(KFM2G16Q2A-DEBx)

- 160 -

FLASH MEMORY

MuxOneNAND4G(KFN4G16Q2A-DEBx)

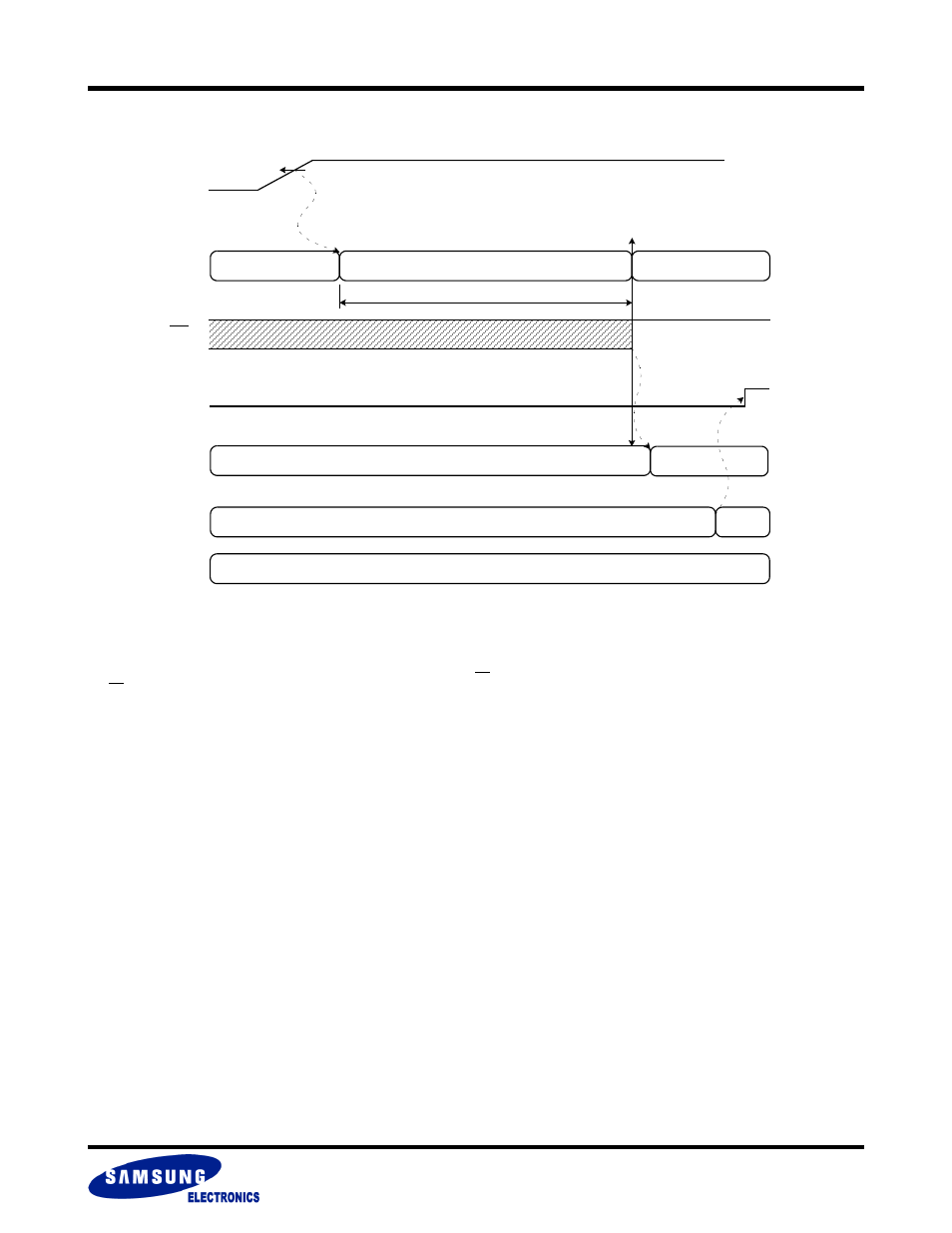

6.17 Cold Reset Timing

NOTE :

1) Bootcode copy operation starts 400us later than POR activation.

The system power should reach Vcc after POR triggering level(typ. 1.5V) within 400us for valid boot code data.

2) 1K bytes Bootcode copy takes 70us(estimated) from sector0 and sector1/page0/block0 of NAND Flash array to BootRAM.

Host can read Bootcode in BootRAM(1K bytes) after Bootcode copy completion.

3) INT register goes ‘Low’ to ‘High’ on the condition of ‘Bootcode-copy done’ and RP rising edge.

If RP goes ‘Low’ to ‘High’ before ‘Bootcode-copy done’, INT register goes to ‘Low’ to ‘High’ as soon as ‘Bootcode-copy done’

System Power

Sleep

Bootcode copy

Idle

Bootcode - copy done

POR triggering level

3)

2)

RP

INT

MuxOneNAND

Operation

0 (default)

1

IOBE bit

1 (default)

INTpol bit

High-Z

1)

INT bit

0 (default)

1