Samsung MUXONENAND A-DIE KFM2G16Q2A User Manual

Page 128

MuxOneNAND2G(KFM2G16Q2A-DEBx)

- 128 -

FLASH MEMORY

MuxOneNAND4G(KFN4G16Q2A-DEBx)

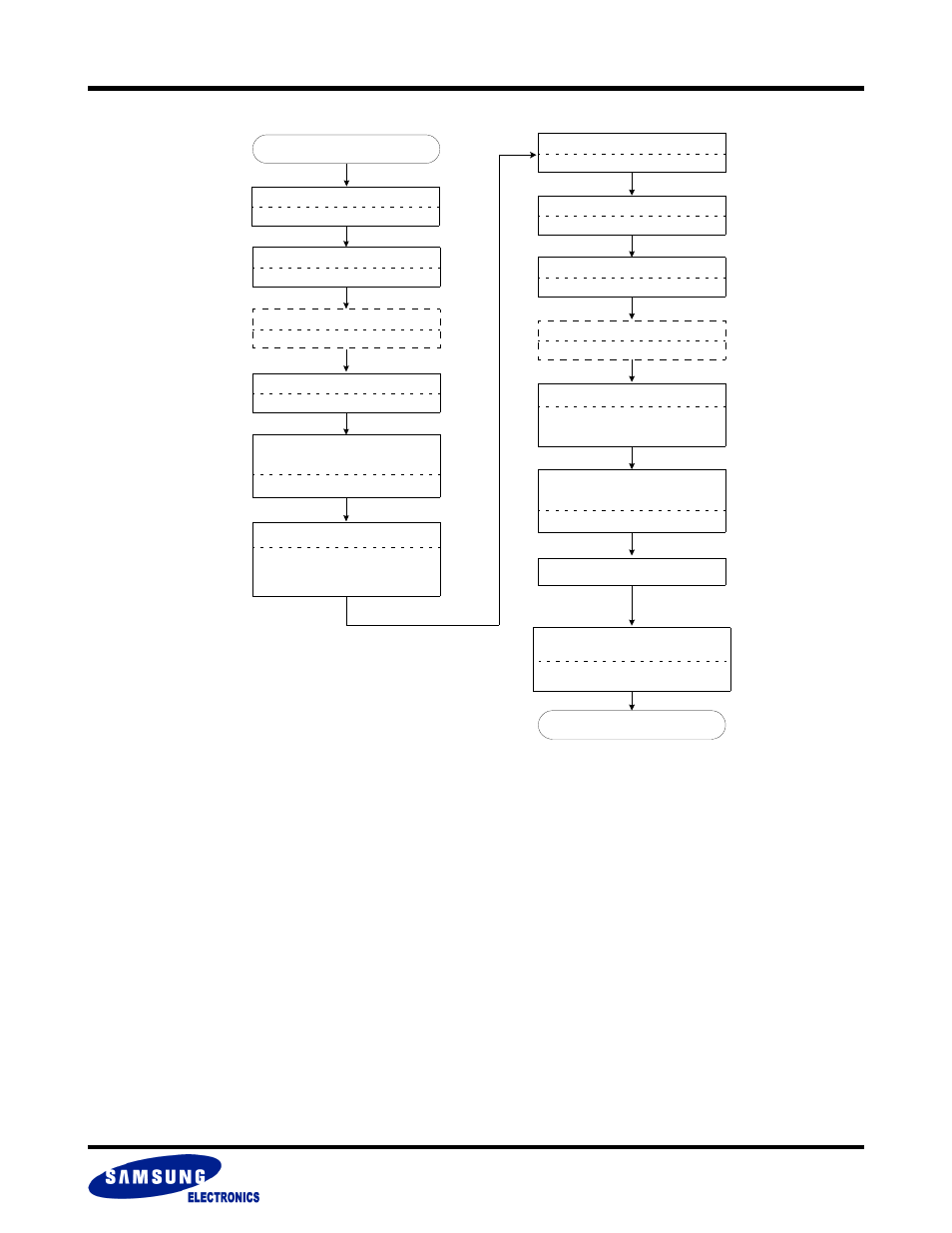

1st Block OTP Lock Operation Flow Chart

NOTE :

1) FBA(NAND Flash Block Address) could be omitted or any address.

2) Data input could be done anywhere between "Start" and "Write Program Command".

3) FBA should point the unlocked area address among NAND Flash Array address map.

4) ‘Write 0 to interrupt register’ step may be ignored when using INT auto mode. Refer to chapter 2.8.18.1.

* DBS, DFS is for DDP

Start

Write ’FPA, FSA’ of Flash

Add: F107h DQ=0000h

Write ’BSA, BSC’ of DataRAM

Add: F200h DQ=0801h/0C01h

Write Data into DataRAM

2)

Add: 8th Word

Write Program command

DQ=0080h or 001Ah

Wait for INT register

low to high transition

Add: F241h DQ[15]=INT

Add: F220h

Write 0 to interrupt register

4)

Add: F241h DQ=0000h

Automatically

updated

DQ=XXF3h

in sector0/spare/page0

1st Block OTP lock completed

Write ’DFS, FBA’ of Flash

Add: F100h DQ=DFS, FBA

3)

Write ’OTP Access’ Command

Add: F220h DQ=0065h

Wait for INT register

Add: F241h DQ[15]=INT

low to high transition

Write 0 to interrupt register

4)

Add: F241h DQ=0000h

Do Cold reset

Write ‘DFS’, ‘FBA’ of Flash

1)

Add: F100h DQ=DFS, FBA

Update Controller

Add: F240h

Status Register

DQ[5]=1(OTP

BL

)

(DBS and DFS must be 0)

Select DataRAM for DDP

Add: F101h DQ=DBS*