Samsung MUXONENAND A-DIE KFM2G16Q2A User Manual

Page 64

MuxOneNAND2G(KFM2G16Q2A-DEBx)

- 64 -

FLASH MEMORY

MuxOneNAND4G(KFN4G16Q2A-DEBx)

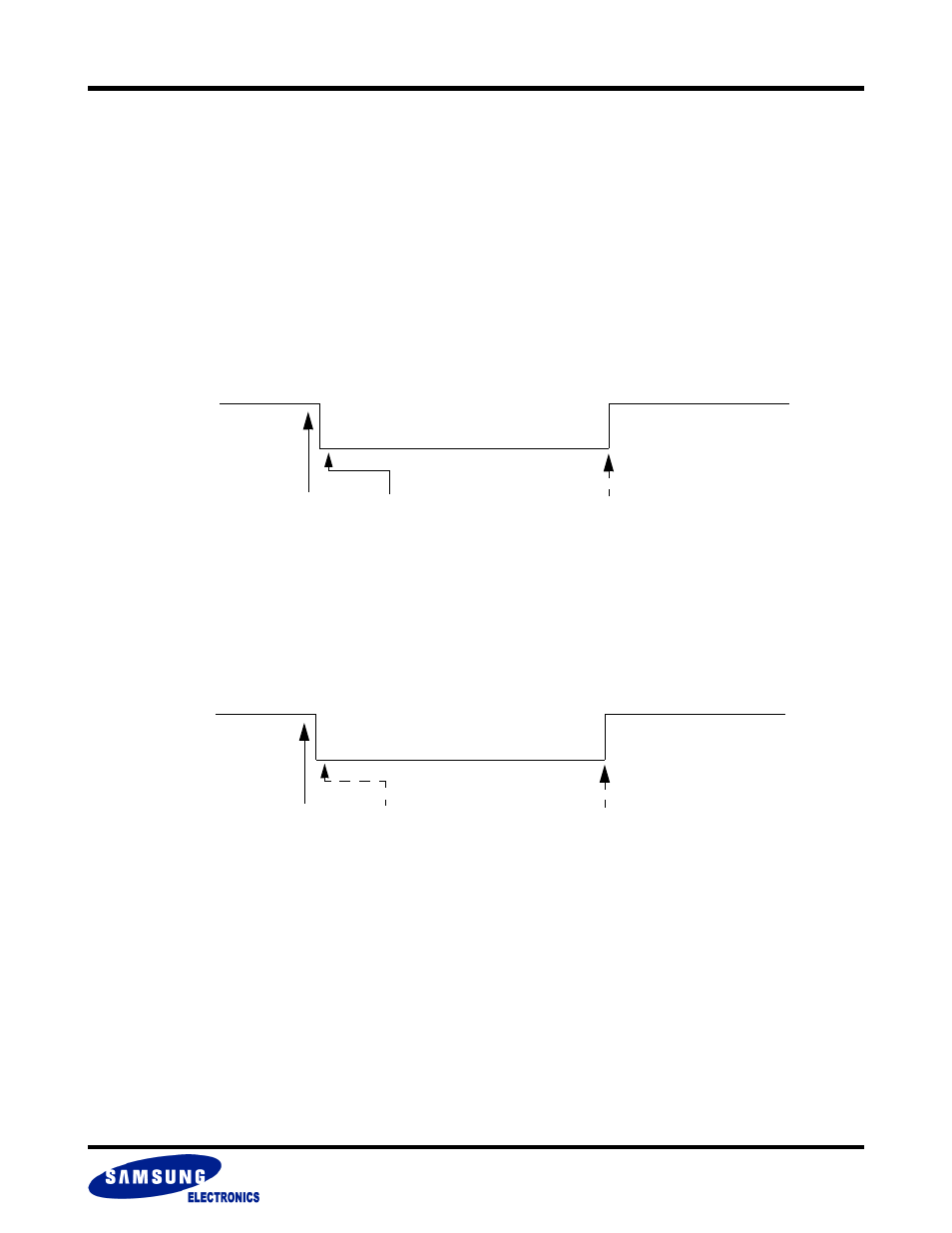

2.8.18.1 Two Methods to Clear Interrupt Register in Command Input

To clear Interrupt Register in command input, user may select one from either following methods.

First method is to turn INT low by manually writing 0000h to INT bit of Interrupt Register.

1)

Second method is input command while INT is high, and the device will automatically turn INT to low.

1)

(Second method is equivalent with method used in general NAND Flash)

User may choose the desirable method to clear Interrupt Register.

Method 1: Manually set INT=0 before writing command into Command Register: Manual INT Mode

(1) Clear Interrupt Register (F241h) by writing 0000h into INT bit of Interrupt Register. This operation will make INT pin turn low.

1)

(2) Write command into Command Register. This will make the device to perform the designated operation.

(3) INT pin will turn back to high once the operation is completed.

1)

NOTE : 1) INT pin polarity is based on ‘IOBE=1 and INT pol=1 (default)’ setting

Method 2: Write command into Command Register at INT ready state: Auto INT Mode

(1) Write command into Command Register. This will automatically turn INT from high to low.

1)

(2) INT pin will turn back to high once the operation is completed.

1)

NOTE : 1) INT pin polarity is based on ‘IOBE=1 and INT pol=1 (default)’ setting

Write 0 into

INT bit of

Interrupt Register

Write command into

Command Register

INT will automatically turn to high

when designated operation is completed.

INT pin1)

INT bit

Write command into

Command Register

INT will automatically

turn to Busy State

INT will automatically turn back to ready state

when designated operation is completed.

INT pin1)

INT bit