3 2x interleave cache program operation – Samsung MUXONENAND A-DIE KFM2G16Q2A User Manual

Page 111

MuxOneNAND2G(KFM2G16Q2A-DEBx)

- 111 -

FLASH MEMORY

MuxOneNAND4G(KFN4G16Q2A-DEBx)

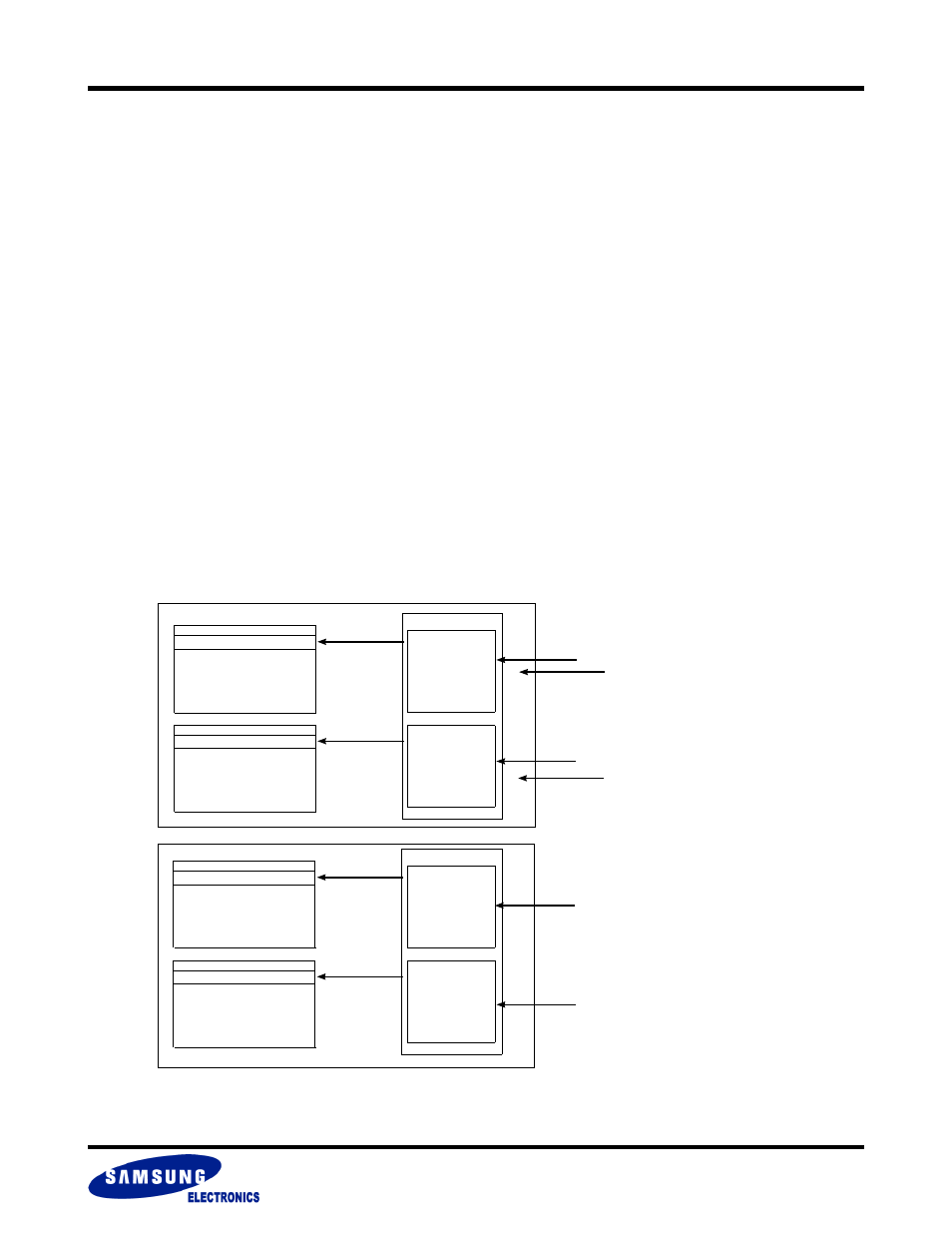

3.11.3 2X Interleave Cache Program Operation

See Timing Diagram 6.15

The 2X Interleave Cache Program is available only on DDP. Host can write data on a chip while programming another chip with this operation.

2X Interleave Cache Program is executed as following:

1. 4KB Data are written from host to DataRAMs in Chip1.

2. 2X Cache Program command issues. This will turn INT bit to busy state

1)

, OnGo bit sets to ‘1’.

(Note that before issuing ‘2X Cache Program Command’, host should make sure that the target blocks are unlocked.)

3. 4KB data will be trasfered to each page buffer in two-plane NAND Flash Array at the same time.

4. While these data are transferring, Host can write another 4KB Data to DataRAM in Chip2.

5. When the transfer operation is completed, programming into NAND Flash Array will automatically start, and at the same time, INT bit will

turn to ‘1’ to indicate that DataRAMs are now ready to be written with next 4KB data.

6. Second 4KB is writable on Chip1 when INT1 goes to ‘1’.

7. When second 4KB is written to two DataRAMs of Chip1, another 2X Cache Program command is issued and INT1 bit will go to ‘0’

1)

again.

NOTE :

1) This is for INT auto mode, for INT manual mode case, user should write 0 to INT bit before issuing any command.

When INT bit goes to ‘1’ after second data transfer from DataRAMs to Page Buffers are completed, user may check the Status Register to

check the 2X program status. During 2X Cache Program, Plane1/2 previous bit shows the status of previous program operation.

For the final 4KB program of 2X Interleave Cache Program scheme, host should issue 2X Program Command(007Dh) on each chip. If the

host issues 007Dh on only a chip, another chip will be on operation as it isn’t finished. Ongo status bit will show the ongoing status of each

chip. Its operation is same as 2X Cache Program operation on each chip. Error bit will show the pass/fail status of each chip of 2X Interleave

Cache program, and Plane1 previous[4] ~ Plane2 current[1] bit will show where the error occured accordingly .

Note that OTP block and 1st block OTP cannot be 2X Interleave Cache Programmed.

Page A

2) Program

2) Program

DataRAM1

1) Data Write

1) Data Write

5) Data Write

(during step 4) when INT1 bit goes to ‘1’)

5) Data Write

DataRAM0

Page B

Plane1

Plane2

Page A

4) Program

4) Program

DataRAM1

3) Data Write

DataRAM0

Page B

Plane1

Plane2

Chip2

Chip1

(during step 4) when INT1 bit goes to ‘1’)

(during step 2) when INT2 bit is on ‘1’)

3) Data Write

(during step 2) when INT2 bit is on ‘1’)