19 system configuration 1 register f221h (r, r/w) – Samsung MUXONENAND A-DIE KFM2G16Q2A User Manual

Page 65

MuxOneNAND2G(KFM2G16Q2A-DEBx)

- 65 -

FLASH MEMORY

MuxOneNAND4G(KFN4G16Q2A-DEBx)

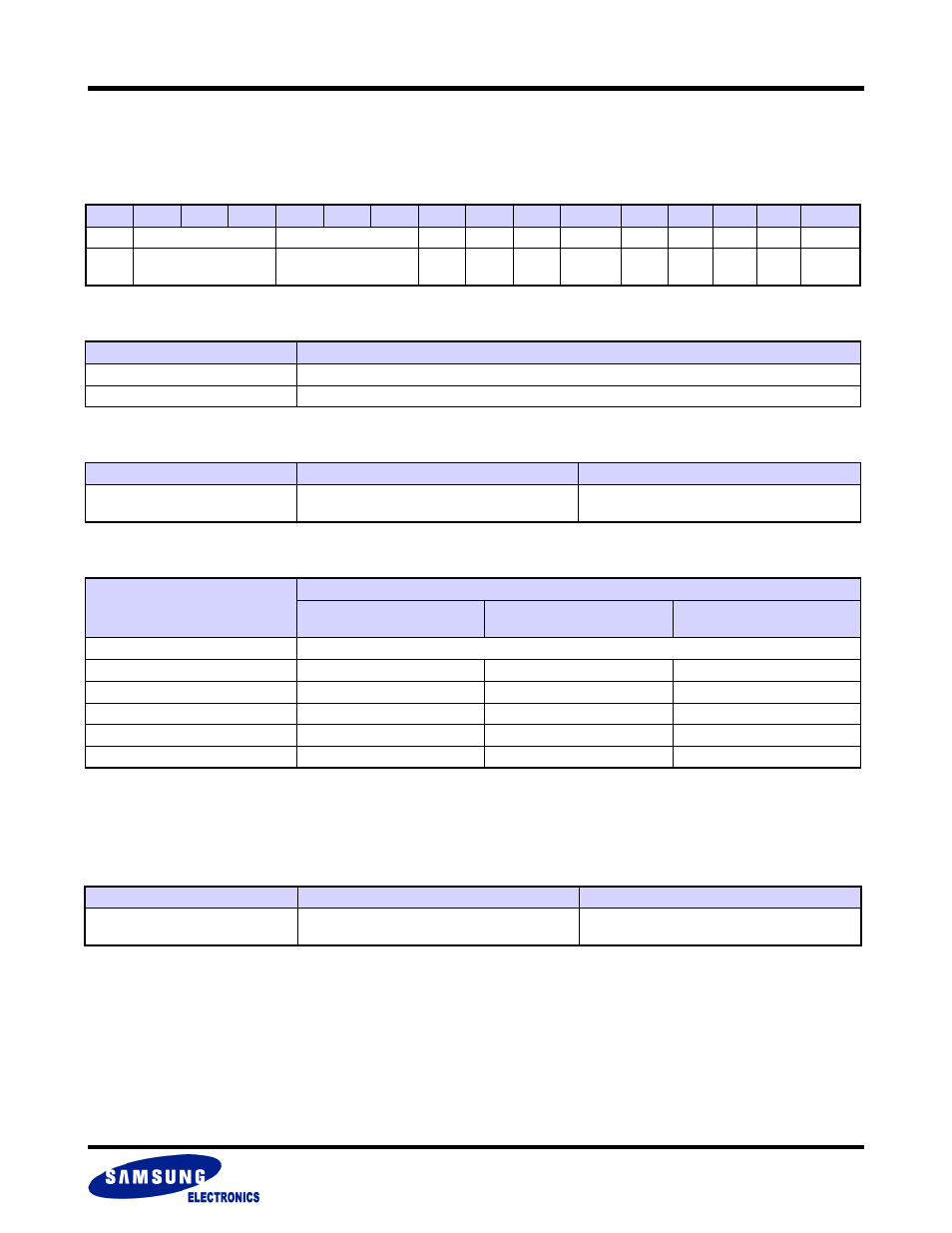

2.8.19 System Configuration 1 Register F221h (R, R/W)

This Read/Write register describes the system configuration.

F221h, default = 40C0h

Read Mode (RM)

Read Mode Information[15]

Burst Read Write Latency (BRWL)

* Default value of BRWL and HF value is BRWL=4, HF=0.

For host frequency over 66MHz, BRWL should be 6 or 7 while HF is 1.

For host frequency range of 40MHz~66MHz, BRWL should be set to 4~7 while HF is 0.

For host frequency under 40MHz, BRWL should be set to 3~7 while HF is 0.

Burst Read Write Latency (BRWL) Information[14:12]

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

R/W

R/W

R

RM

BRWL

BL

ECC

RDY

pol

INT

pol

IOBE

RDY

Conf

Reserv

ed

HF

WM

BWPS

RM

Read Mode

0

Asynchronous read(default)

1

Synchronous read

Item

Definition

Description

RM

Read Mode

Selects between asynchronous read mode and

synchronous read mode

BRWL

Latency Cycles (Read/Write)

under 40MHz

(HF=0)

40MHz~66MHz

(HF=0)

over 66MHz

(HF=1)

000~010

Reserved

011

3(up to 40MHz. min)

3(N/A)

3(N/A)

100 (default)

4

4(min.)

4(N/A)

101

5

5

5(N/A)

110

6

6

6(min.)

111

7

7

7

Item

Definition

Description

BRWL

Burst Read Latency /

Burst Write Latency

Specifies the access latency in the burst

read / write transfer for the initial access