26 ecc status register ff00h (r) – Samsung MUXONENAND A-DIE KFM2G16Q2A User Manual

Page 78

MuxOneNAND2G(KFM2G16Q2A-DEBx)

- 78 -

FLASH MEMORY

MuxOneNAND4G(KFN4G16Q2A-DEBx)

2.8.26 ECC Status Register FF00h (R)

This Read register shows the Error Correction Status. The MuxOneNAND can detect 1- or 2-bit errors and correct 1-bit errors. 3-bit or more

error detection and correction is not supported.

ECC can be performed on the NAND Flash main and spare memory areas. The ECC status register can also show the number of errors in a

sector as a result of an ECC check in during a load operation. ECC status bits are also updated during a boot loading operation.

ECC registers will be reset when another command is issued.

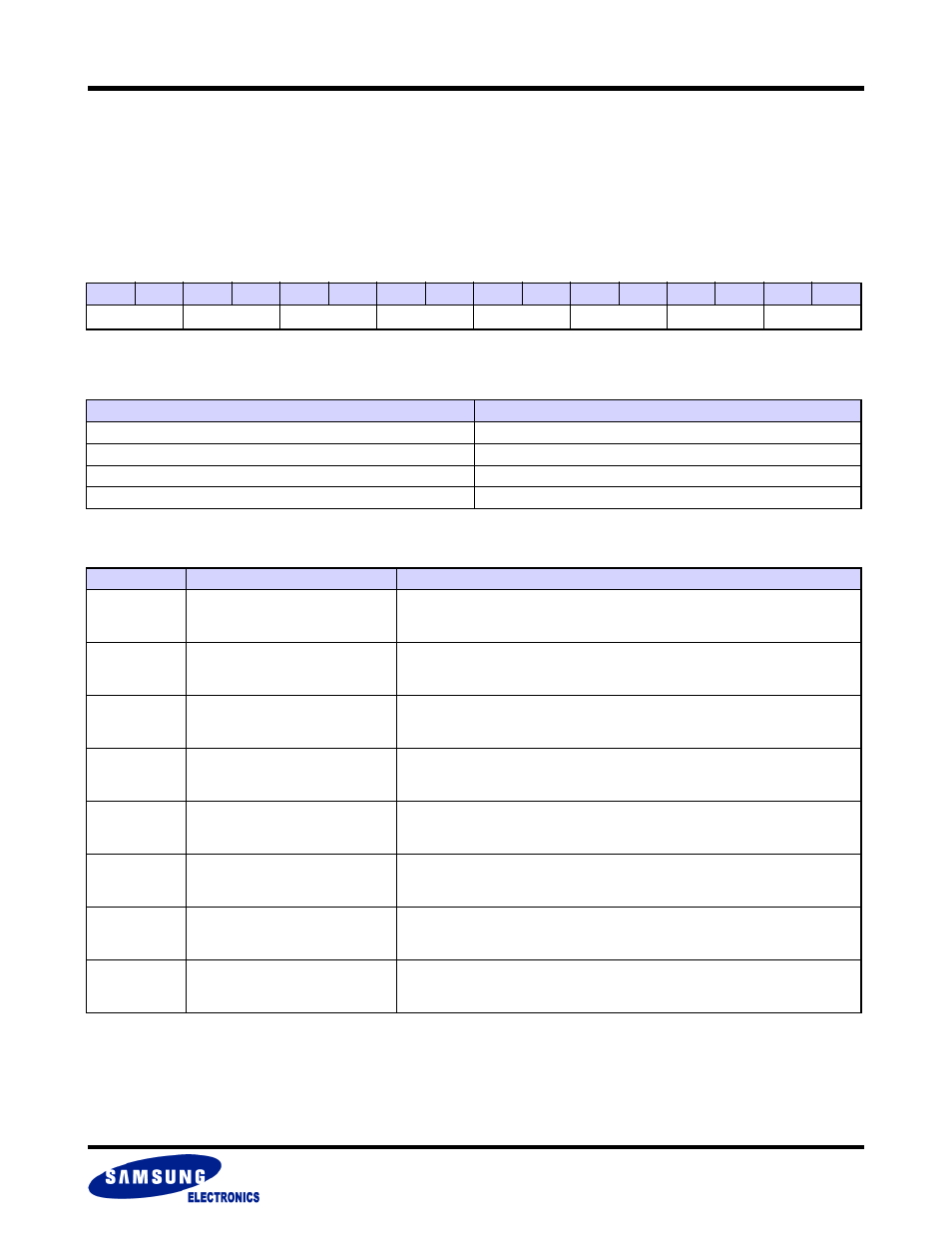

FF00h, default = 0000h

NOTE :

1) After Synchronous Block Burst Read operation, DQ[0] shows accmulated 1bit error.

Error Status

ECC Information[15:0]

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ERm3

ERs3

ERm2

ERs2

ERm1

ERs1

ERm0

ERs0

1)

ERm, ERs

ECC Status

00

No Error

01

1 bit error(correctable)

10

2 bit error (uncorrectable)

11

Reserved

Item

Definition

Description

ERm0

1st selected sector of

the main BufferRAM

Status of errors in the 1st selected sector of the main BufferRAM

as a result of an ECC check during a load operation.

Also updated during a Bootload operation.

ERm1

2nd selected sector of

the main BufferRAM

Status of errors in the 2nd selected sector of the main BufferRAM

as a result of an ECC check during a load operation.

Also updated during a Bootload operation.

ERm2

3rd selected sector of

the main BufferRAM

Status of errors in the 3rd selected sector of the main BufferRAM

as a result of an ECC check during a load operation.

Also updated during a Bootload operation.

ERm3

4th selected sector of

the main BufferRAM

Status of errors in the 4th selected sector of the main BufferRAM

as a result of an ECC check during a load operation.

Also updated during a Bootload operation.

ERs0

1st selected sector of

the spare BufferRAM

Status of errors in the 1st selected sector of the spare BufferRAM

as a result of an ECC check during a load operation.

Also updated during a Bootload operation.

ERs1

2nd selected sector of

the spare BufferRAM

Status of errors in the 2nd selected sector of the spare BufferRAM

as a result of an ECC check during a load operation.

Also updated during a Bootload operation.

ERs2

3rd selected sector of

the spare BufferRAM

Status of errors in the 3rd selected sector of the spare BufferRAM

as a result of an ECC check during a load operation.

Also updated during a Bootload operation.

ERs3

4th selected sector of

the spare BufferRAM

Status of errors in the 4th selected sector of the spare BufferRAM

as a result of an ECC check during a load operation.

Also updated during a Bootload operation.