1 the int pin to a host general purpose i/o – Samsung MUXONENAND A-DIE KFM2G16Q2A User Manual

Page 167

MuxOneNAND2G(KFM2G16Q2A-DEBx)

- 167 -

FLASH MEMORY

MuxOneNAND4G(KFN4G16Q2A-DEBx)

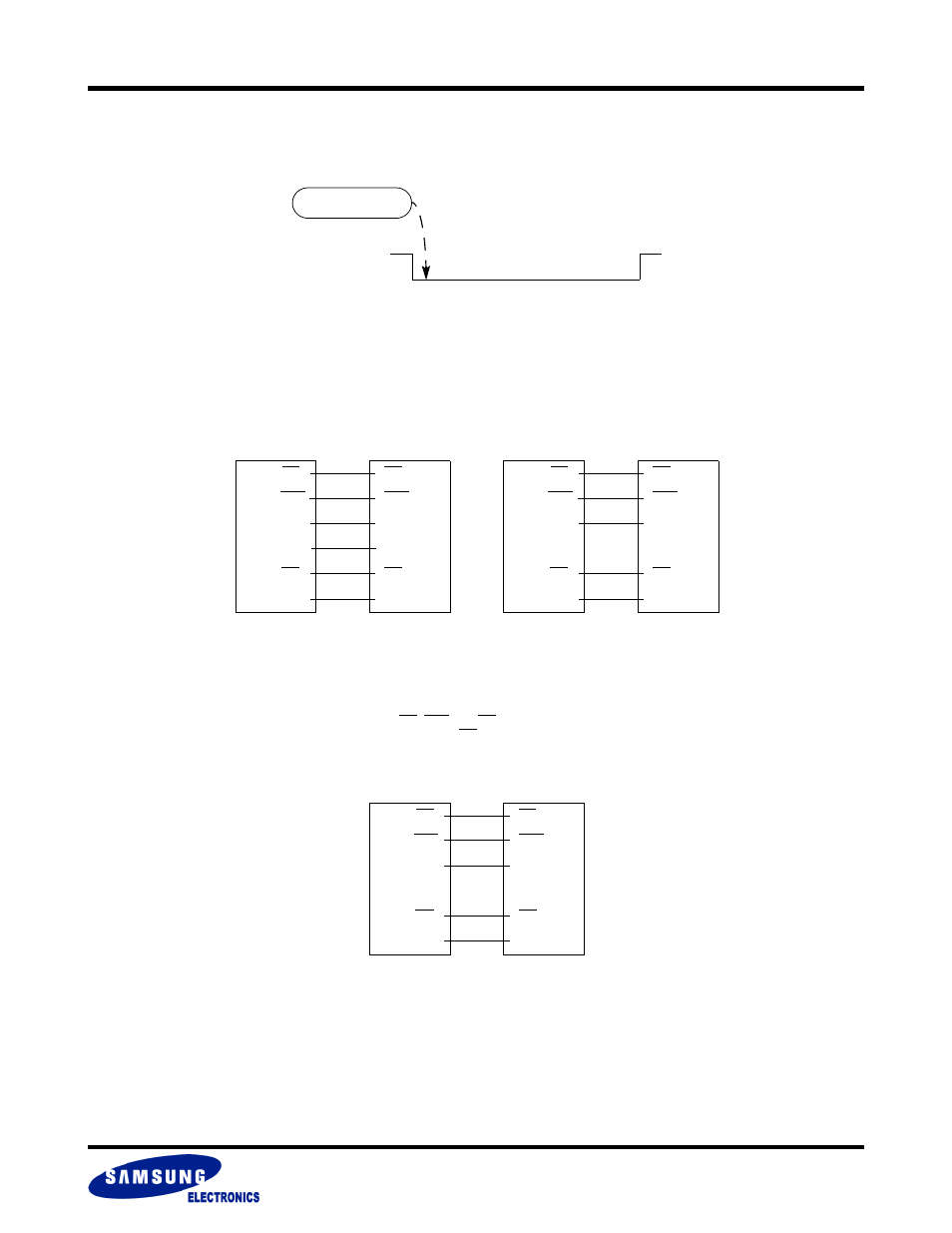

7.1.1 The INT Pin to a Host General Purpose I/O

INT can be tied to a Host GPIO to detect the rising edge of INT, signaling the end of a command operation.

This can be configured to operate either synchronously or asynchronously as shown in the diagrams below.

Synchronous Mode Using the INT Pin

When operating synchronously, INT is tied directly to a Host GPIO. RDY could be connected as one of following guides.

Asynchronous Mode Using the INT Pin

When configured to operate in an asynchronous mode, CE, AVD and OE of the MuxOneNAND are tied to corresponding pins of the Host.

CLK is tied to the Host Vss (Ground). RDY is tied to a no-connect. OE of the MuxOneNAND and Host are tied together and INT is tied to a

GPIO.

INT

COMMAND

Host

MuxOneNAND

RDY(WAIT)

OE

CLK

CE

RDY

OE

CLK

CE

AVD

GPIO

INT

Host

MuxOneNAND

OE

CLK

CE

RDY

OE

CLK

CE

AVD

GPIO

INT

Handshaking Mode

Non-Handshaking Mode

AVD

AVD

Host

MuxOneNAND

OE

Vss

CE

RDY

OE

CLK

CE

AVD

GPIO

INT

AVD