Sfr definition 9.7. ie: interrupt enable – Silicon Laboratories C8051F347 User Manual

Page 91

Rev. 1.3

91

C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

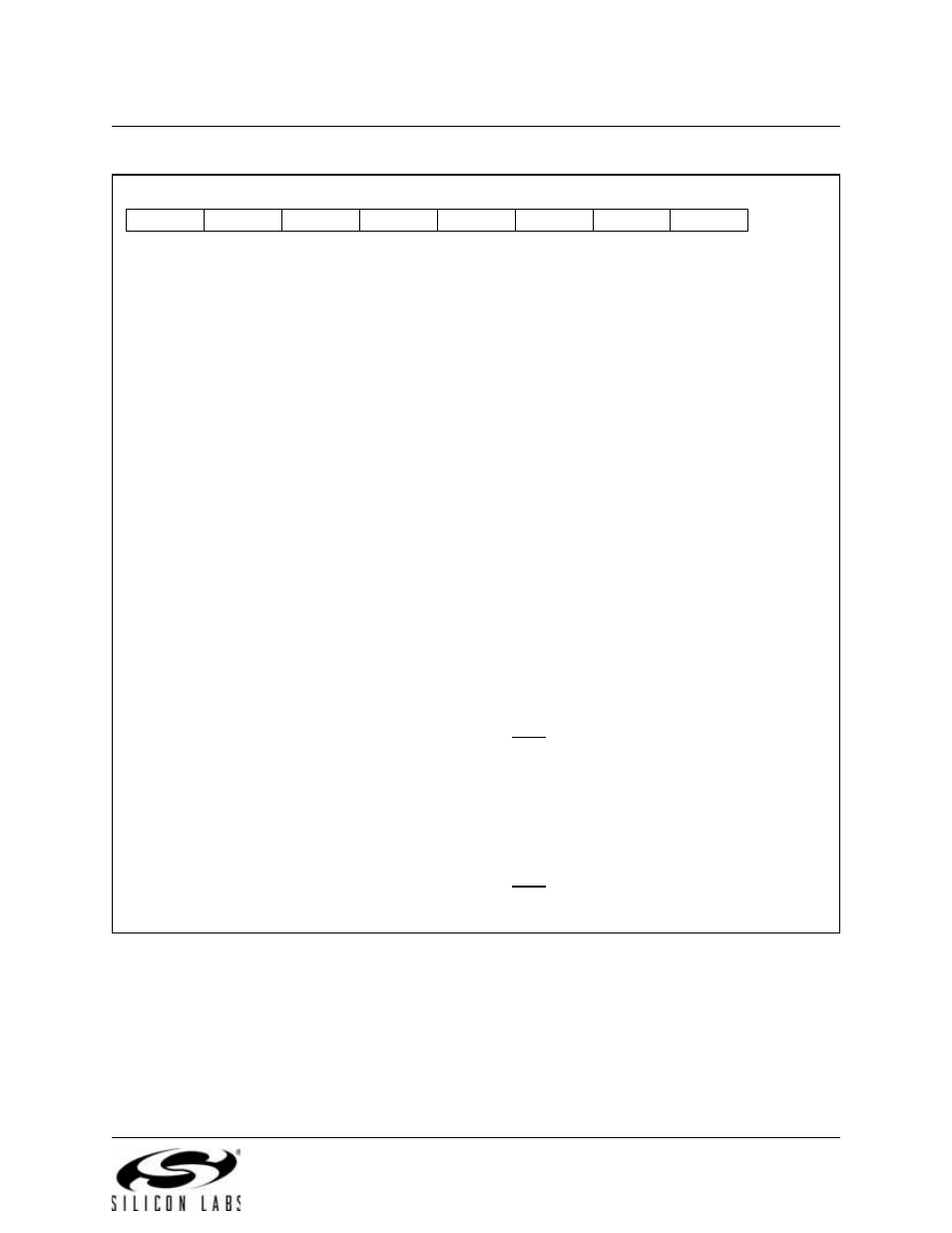

SFR Definition 9.7. IE: Interrupt Enable

Bit7:

EA: Enable All Interrupts.

This bit globally enables/disables all interrupts. It overrides the individual interrupt mask set-

tings.

0: Disable all interrupt sources.

1: Enable each interrupt according to its individual mask setting.

Bit6:

ESPI0: Enable Serial Peripheral Interface (SPI0) Interrupt.

This bit sets the masking of the SPI0 interrupts.

0: Disable all SPI0 interrupts.

1: Enable interrupt requests generated by SPI0.

Bit5:

ET2: Enable Timer 2 Interrupt.

This bit sets the masking of the Timer 2 interrupt.

0: Disable Timer 2 interrupt.

1: Enable interrupt requests generated by the TF2L or TF2H flags.

Bit4:

ES0: Enable UART0 Interrupt.

This bit sets the masking of the UART0 interrupt.

0: Disable UART0 interrupt.

1: Enable UART0 interrupt.

Bit3:

ET1: Enable Timer 1 Interrupt.

This bit sets the masking of the Timer 1 interrupt.

0: Disable all Timer 1 interrupt.

1: Enable interrupt requests generated by the TF1 flag.

Bit2:

EX1: Enable External Interrupt 1.

This bit sets the masking of External Interrupt 1.

0: Disable external interrupt 1.

1: Enable interrupt requests generated by the INT1 input.

Bit1:

ET0: Enable Timer 0 Interrupt.

This bit sets the masking of the Timer 0 interrupt.

0: Disable all Timer 0 interrupt.

1: Enable interrupt requests generated by the TF0 flag.

Bit0:

EX0: Enable External Interrupt 0.

This bit sets the masking of External Interrupt 0.

0: Disable external interrupt 0.

1: Enable interrupt requests generated by the INT0 input.

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Reset Value

EA

ESPI0

ET2

ES0

ET1

EX1

ET0

EX0

00000000

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

SFR Address:

(bit addressable)

0xA8